#### INFORMATION TO USERS

This reproduction was made from a copy of a document sent to us for microfilming. While the most advanced technology has been used to photograph and reproduce this document, the quality of the reproduction is heavily dependent upon the quality of the material submitted.

The following explanation of techniques is provided to help clarify markings or notations which may appear on this reproduction.

- 1. The sign or "target" for pages apparently lacking from the document photographed is "Missing Page(s)". If it was possible to obtain the missing page(s) or section, they are spliced into the film along with adjacent pages. This may have necessitated cutting through an image and duplicating adjacent pages to assure complete continuity.

- 2. When an image on the film is obliterated with a round black mark, it is an indication of either blurred copy because of movement during exposure, duplicate copy, or copyrighted materials that should not have been filmed. For blurred pages, a good image of the page can be found in the adjacent frame. If copyrighted materials were deleted, a target note will appear listing the pages in the adjacent frame.

- 3. When a map, drawing or chart, etc., is part of the material being photographed, a definite method of "sectioning" the material has been followed. It is customary to begin filming at the upper left hand corner of a large sheet and to continue from left to right in equal sections with small overlaps. If necessary, sectioning is continued again—beginning below the first row and continuing on until complete.

- 4. For illustrations that cannot be satisfactorily reproduced by xerographic means, photographic prints can be purchased at additional cost and inserted into your xerographic copy. These prints are available upon request from the Dissertations Customer Services Department.

- 5. Some pages in any document may have indistinct print. In all cases the best available copy has been filmed.

|  | , |  |

|--|---|--|

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  | , |  |

|  |   |  |

#### Hooper, Richard Preston

AN APPLICATION OF KNOWLEDGE-BASED SYSTEMS TO ELECTRONIC COMPUTER-AIDED ENGINEERING, DESIGN, AND MANUFACTURING DATA BASE TRANSPORT

University of California, Los Angeles

Ph.D. 1985

University

Microfilms

International 300 N. Zeeb Road, Ann Arbor, Mf 48106

Copyright 1985

by

Hooper, Richard Preston

All Rights Reserved

|  |  | • |

|--|--|---|

|  |  |   |

## UNIVERSITY OF CALIFORNIA Los Angeles

An Application of Knowledge-Based Systems to Electronic Computer-Aided Engineering, Design, and Manufacturing Data Base Transport

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Computer Science

by

Richard Preston Hooper

The dissertation of Richard Preston Hooper is approved.

Kirby A. Baker

Belliam Densell

R. K. Samu

Rakesh K. Sarin

Chand R. Viswanatian

Chand R. Viswanathan

Michel A. Melkanoff, Committee Chair

University of California, Los Angeles

1985

© Copyright by

Richard Preston Hooper

1985

### **DEDICATION**

To my wife,

Denise

whose love and companionship have sustained me, and who has shared this experience with me.

To my children,

Jacquelyn and Douglas

who have brought joy and

laughter into my life.

To my parents,

Fred and Shirley

who have always had faith in me, and who have been a never ceasing source of encouragement.

## TABLE OF CONTENTS

|                                                                                              | Page            |

|----------------------------------------------------------------------------------------------|-----------------|

|                                                                                              |                 |

| 1 INTRODUCTION                                                                               | 1               |

| 2 CAE/CAD/CAM ENVIRONMENT 2.1 Custom VLSI or Gate Array                                      | 8               |

| 2.1 Custom VLSI or Gate Array                                                                | 9               |

| 2.2 Printed Circuit Boards                                                                   | 15              |

| 2.3 CAE/CAD/CAM Tools 2.4 CAE/CAD/CAM Data for Electronic Design                             | 18<br>22        |

| 2.4 CAE/CAD/CAM Data For Electronic Design                                                   | 31              |

| 2.5 CAE/CAD/CAM Data Exchange Standards 2.5.1 Initial Graphics Exchange Specification (IGES) | 33              |

| 2.5.2 ANSI/IPC-D-350                                                                         | 38              |

| 2.5.2 ANSI/IPC-D-350                                                                         | 40              |

| 2.5.4 Commercial Systems                                                                     | 41              |

| 3 DATA TRANSPORT METHODOLOGY                                                                 | 43              |

| 3.1 Media Difficulties                                                                       | 43              |

| 3.1 Media Difficulties                                                                       | 44              |

| 3.3 Database Organization Differences                                                        | 46              |

| 3.4 General Approach 3.5 System Architecture                                                 | 52              |

| 3.5 System Architecture                                                                      | 74              |

| 3.5.1 Compiler / DBIF                                                                        | 77<br>78        |

| 3.5.3 Translata Engina                                                                       | 80              |

| 3.5.3 Translate Engine                                                                       | 82              |

| 3.5.5 Formatter                                                                              | 83              |

|                                                                                              |                 |

| 4 PROTOTYPE SYSTEM                                                                           | 85              |

| 4.1 Introduction to Prolog                                                                   | 85              |

| 4.2 Prototype Elements                                                                       | $\frac{92}{92}$ |

| 4.2.2 Data Elements                                                                          | 108             |

| 4.3 Operational Scenario                                                                     | 116             |

| •                                                                                            |                 |

| 5 TEST CASES                                                                                 | 123             |

| 5.1 Hypothetical Cases: DR1 and DR2                                                          | 124             |

| 5.2 TDL to PCB CAD Data Base                                                                 | 138<br>139      |

| 5.2.2 Forward Rules                                                                          | 144             |

| 5.2.3 Reverse Rules                                                                          | 153             |

| 5.2.4 Forward Translation Results                                                            | 157             |

| 5.2.5 Reverse Translation Results                                                            | 161             |

| 5.3 CALMA to CIF                                                                             | 164             |

| 5.3.1 Data Mapping                                                                           | 164             |

| 5.3.2 Forward Rules                                                                          | 177<br>187      |

| 5.3.4 Forward Translation Results                                                            | 189             |

| 5.3.5 Reverse Translation Results                                                            | 193             |

| 6 CONCLUSION                                                   | 198 |

|----------------------------------------------------------------|-----|

| Appendix A GLOSSARY                                            | 203 |

| Appendix B ALTERNATIVE PROTOTYPE IMPLEMENTATIONS               | 208 |

| Appendix C CALMA STREAM FORMAT DATA                            | 211 |

| Appendix D DBIF REPRESENTING CALMA STREAM FORMAT               | 217 |

| Appendix E TDL DBIF                                            | 225 |

| Appendix F DBIF REPRESENTING CIF FILE                          | 227 |

| Appendix G SAMPLE CIF FILE                                     | 233 |

| Appendix H TDL PREPROCESSOR BNF EXCERPT                        | 235 |

| Appendix I SOURCE DBIF FOR CALMA—CIF DATA TRANSPORT CASE       | 243 |

| Appendix J RULES FOR THE CALMA—CIF FORWARD TRANSPORT TEST CASE | 246 |

| Appendix K RULES FOR THE CALMA—CIF REVERSE TRANSPORT TEST CASE | 254 |

| Appendix L GENERIC FACTS CREATED FROM SOURCE TDL               | 260 |

| Appendix M GENERIC FACTS CREATED FROM SOURCE CALMA DATA        | 262 |

| Appendix N CIF DATA OUTPUT FROM GENERIC FACTS                  | 264 |

| Appendix O GENERIC DATA FROM CIF DURING REVERSE TRANSLATION    | 266 |

| Appendix P CALMA OUTPUT DATA FROM REVERSE TRANSLATION          | 269 |

| Appendix Q REVERSE TRANSLATION SYSTEM LOG, CIF TO CALMA        | 271 |

| Appendix R KEPT FACTS FROM CALMA TO CIF TRANSLATION            | 273 |

| References                                                     | 975 |

## LIST OF FIGURES

|                                                                         | rage   |

|-------------------------------------------------------------------------|--------|

| Figure 2.1. Sample System Level Block Diagram                           | 10     |

| Figure 2.2. Typical Electronic Design Flow.                             | 11     |

| Figure 2.3. Multi-level (Hierarchical) Design.                          | 12     |

| Figure 2.4. Sample Schematic Diagram.                                   | 16     |

| Figure 2.5. CAE/CAD/CAM Functions.                                      | 19     |

| Figure 2.6. CAE/CAD/CAM Data Categories                                 | 23     |

| Figure 2.7. Build-Design Data Base Structure.                           | 25     |

| Figure 2.8. Build-Design Data Base for Sample Schematic                 | 26     |

| Figure 2.9. Hewlett-Packard DTS-70 Pin-Signal Data Input Synt           | ax. 27 |

| Figure 2.10. Hughes DEC-20 CAD System Data Base                         | 29     |

| Figure 2.11. Computervision.                                            | 30     |

| Figure 2.12. Comparison of DEC-20 and CV CAD Data Bases                 | 32     |

| Figure 3.1. The Delta Problem.                                          | 45     |

| Figure 3.2. Hierarchical Model.                                         | 47     |

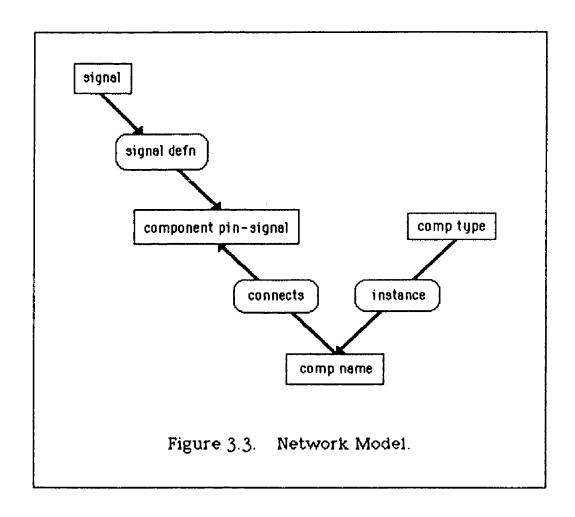

| Figure 3.3. Network Model.                                              | 48     |

| Figure 3.4. Relational Model.                                           | 49     |

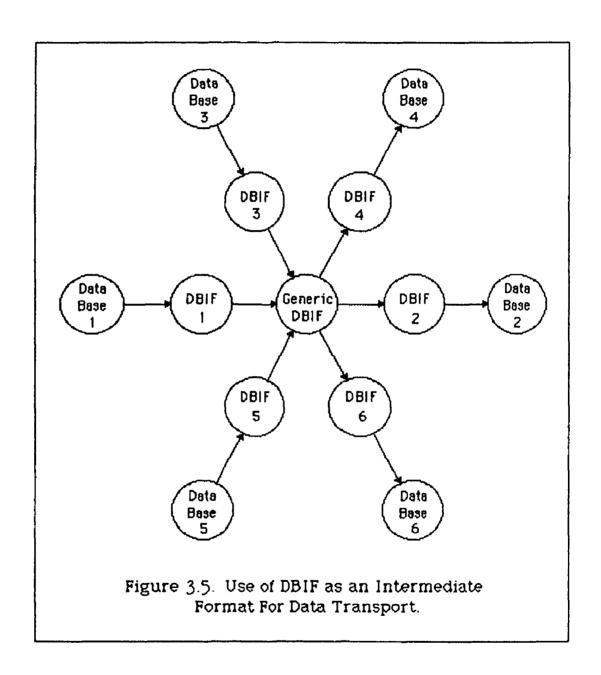

| Figure 3.5. Use of DBIF to Aid in Data Base Transport                   | 55     |

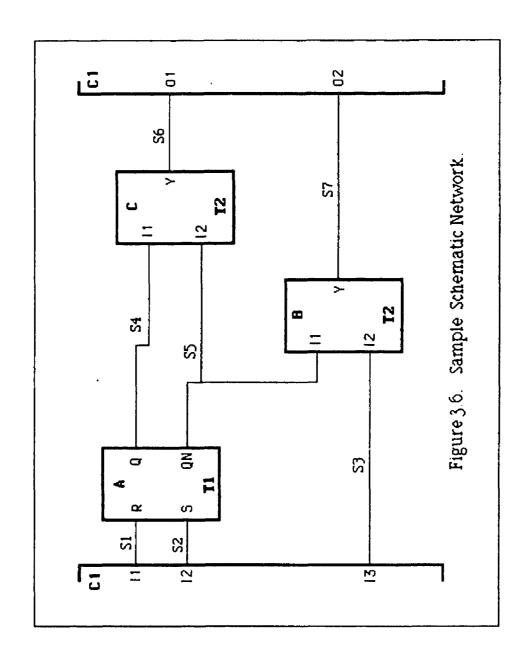

| Figure 3.6. Sample Schematic Network.                                   | 58     |

| Figure 3.7. Data Base Representation 1 (DR1).                           | 59     |

| Figure 3.8. Data Base Representation 2 (DR2).                           | 60     |

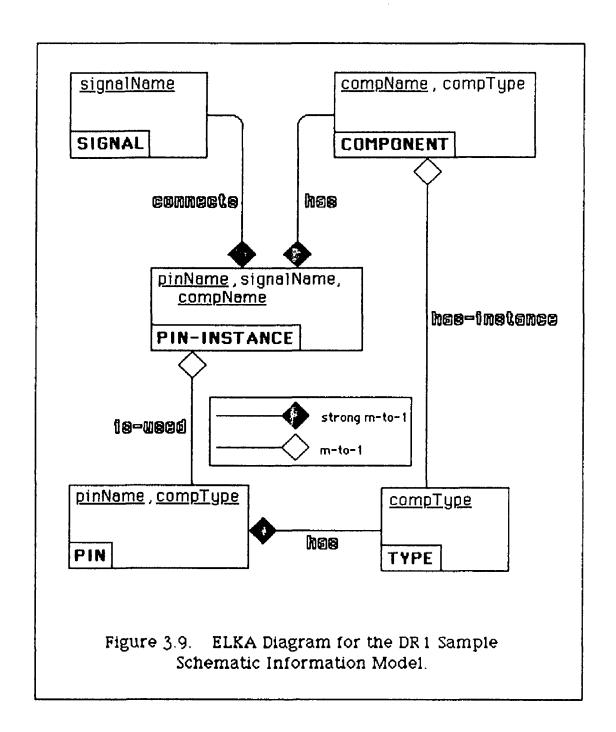

| Figure 3.9. ELKA Diagram for the DR1 Sample Schematic Information Model | 62     |

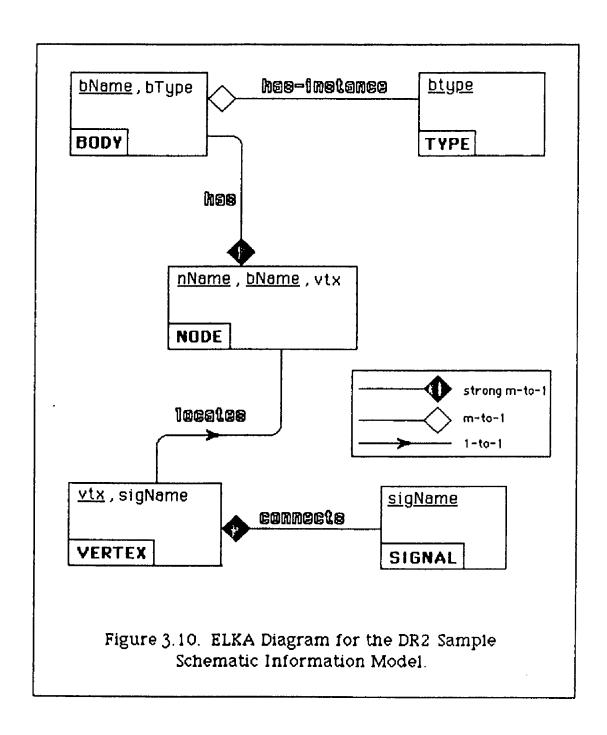

| Figure 3.10. ELKA Diagram for the DR2 Sample Schematic                  | 65     |

| Figure 3.11. Alternative Translation Schemes.                           | 67     |

| Figure 3.12. Translators Needed Using a Generic Data Schema              | 67         |

|--------------------------------------------------------------------------|------------|

| Figure 3.13. DBIF Encoding of DR2 Data.                                  | 70         |

| Figure 3.14. DR2 Relational Data Base.                                   | <b>7</b> 5 |

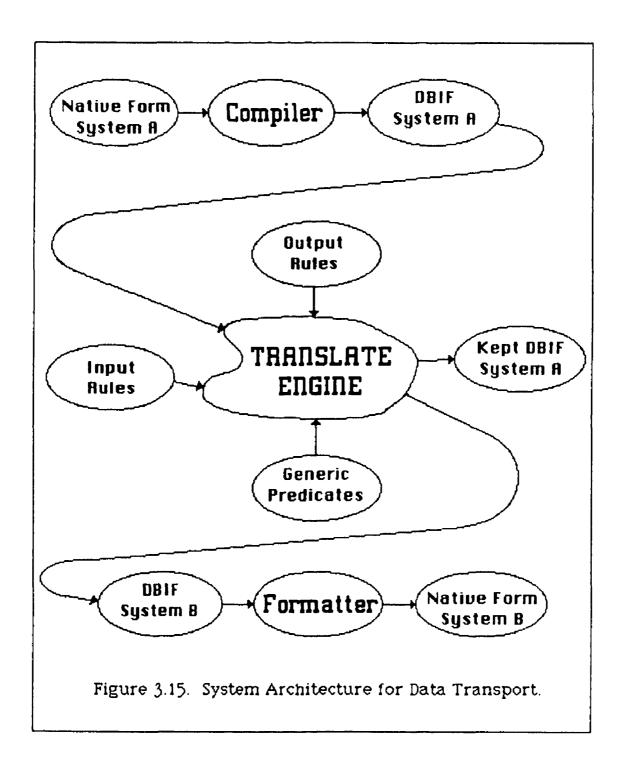

| Figure 3.15. System Architecture for Data Transport                      | 76         |

| Figure 3.16. Sample DBIF Encoding.                                       | 78         |

| Figure 3.17. Generic Predicates for Logical Data.                        | 80         |

| Figure 3.18. Generic Predicates for Physical Data                        | 81         |

| Figure 3.19. Sample Formatter Results.                                   | 84         |

| Figure 4.1. Prolog Terms.                                                | 86         |

| Figure 4.2. Pseudo-BNF description of the CALMA Stream Format.           | 94         |

| Figure 4.3. Sample CALMA Layout.                                         | 95         |

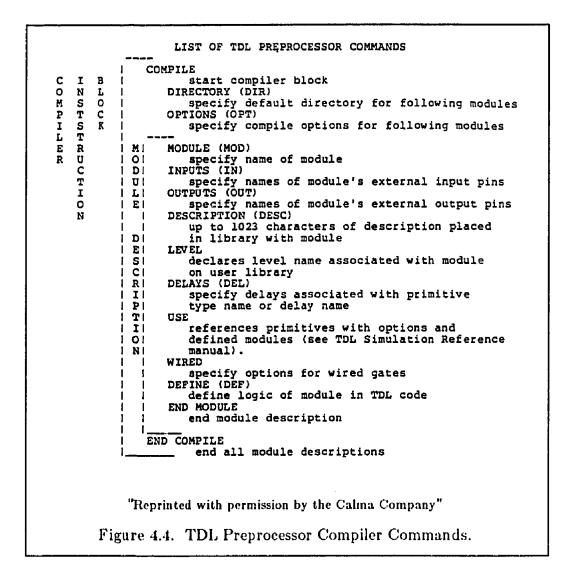

| Figure 4.4. TDL Preprocessor Compiler Commands                           | 97         |

| Figure 4.5. Sample TDL Input.                                            | 98         |

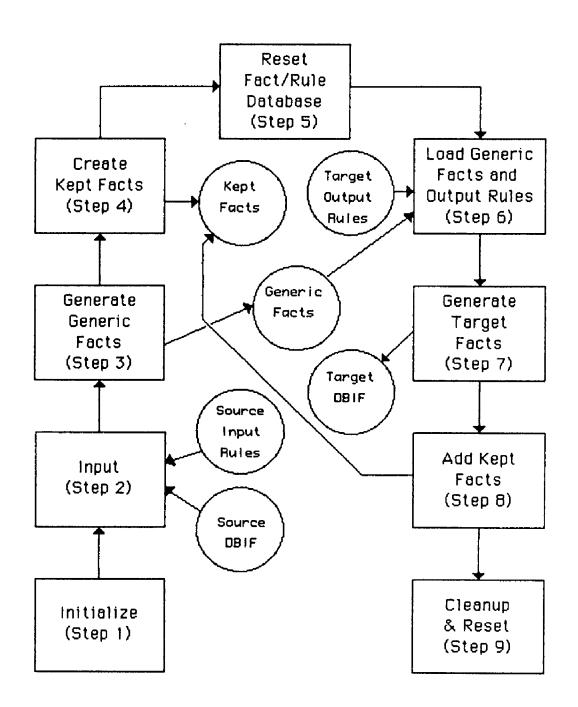

| Figure 4.6. Translate Engine Processing Flow.                            | 100        |

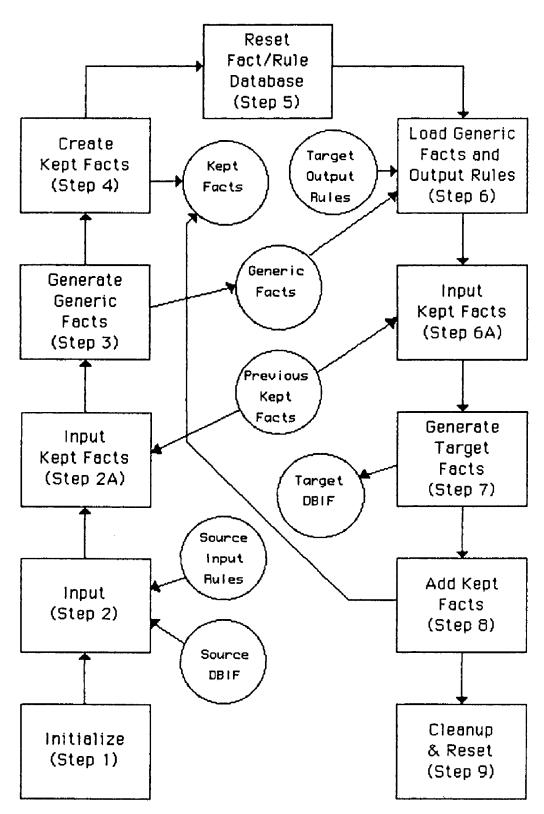

| Figure 4.7. Translate Engine Processing Flow with Kept Facts             | 102        |

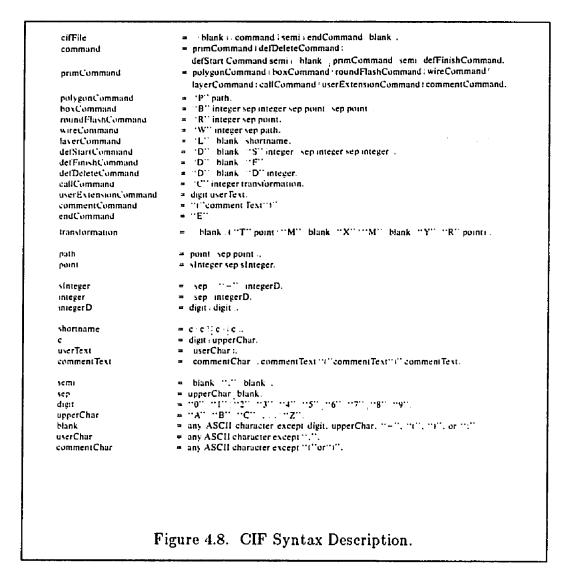

| Figure 4.8. CIF Syntax Description.                                      | 103        |

| Figure 4.9. Sample DBIF for DR1.                                         | 105        |

| Figure 4.10. Prolog Code for the DR1 Formatter                           | 106        |

| Figure 4.11. Tabular Form of DR1 Data.                                   | 106        |

| Figure 4.12. Prolog Encoding of Generic Predicates for Logical Data.     | 109        |

| Figure 4.13. Prolog Encoding of Generic Predicates for Physical Data.    | 110        |

| Figure 4.14. DBIF for Sample DR2 Data Base.                              | 111        |

| Figure 4.15. Mapping of DR2 Terms onto Generic Predicates                | 112        |

| Figure 4.16. Rules for Transforming DR2 into a Generic Form              | 113        |

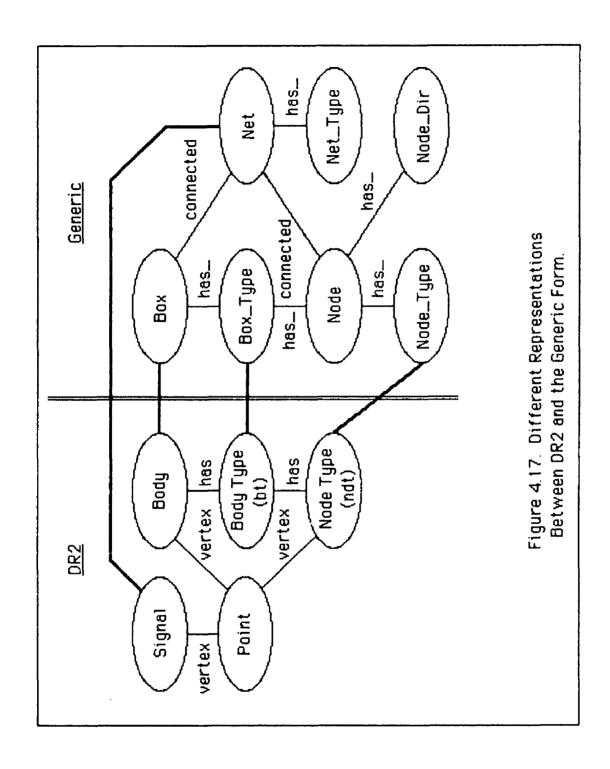

| Figure 4.17. Different Representations Between DR2 and the Generic Form. | 115        |

| Figure 4.18. System Log of the Prototype Execution                      |

|-------------------------------------------------------------------------|

| Figure 4.19. Generic Data Generated by the Prototype Translate Engine.  |

| Figure 4.20. DR1 Target Output Rules.                                   |

| Figure 4.21. Target DR1 DBIF.                                           |

| Figure 4.22. Kept Facts Generated in Transporting Data from DR2 to DR1. |

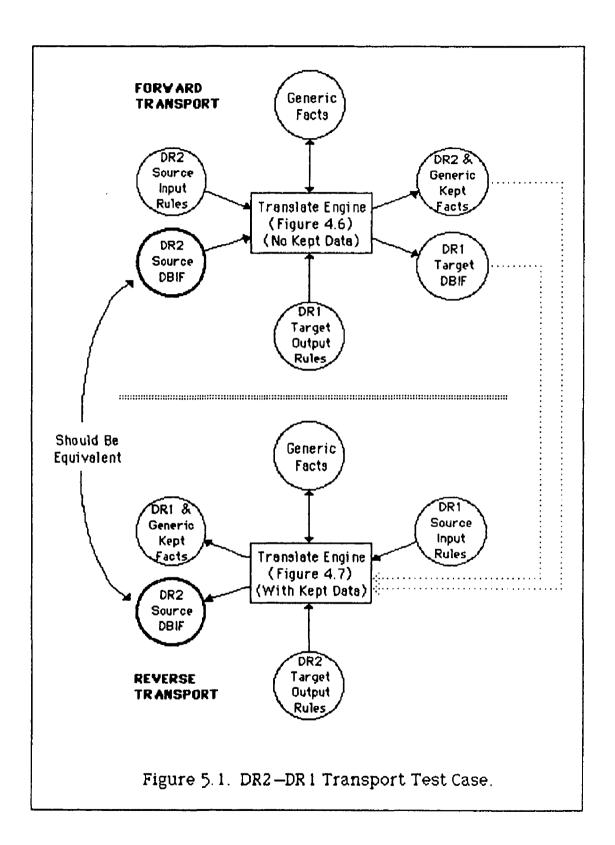

| Figure 5.1. DR2-DR1 Transport Test Case.                                |

| Figure 5.2. Prolog Output for DR2 to DR1 Translation.                   |

| Figure 5.3. Source DR1 DBIF (dr1.dat).                                  |

| Figure 5.4. Source Input Rules for DR1 (dr1in.rul).                     |

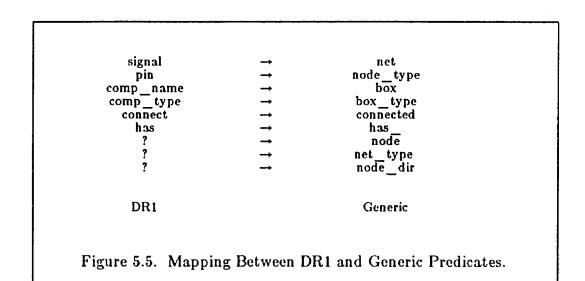

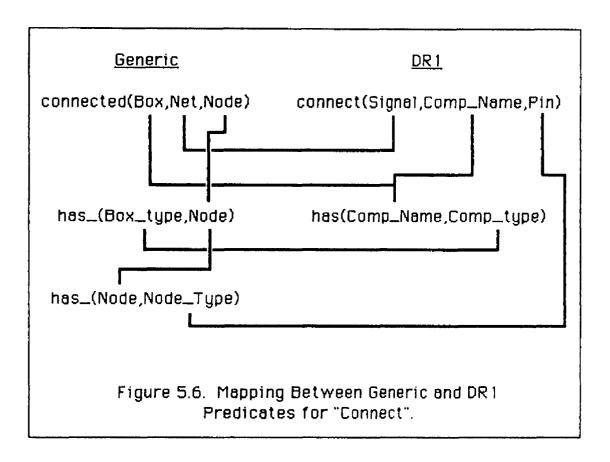

| Figure 5.5. Mapping Between DR1 and Generic Predicates                  |

| Figure 5.6. Mapping Between Generic and DR1 Predicates for              |

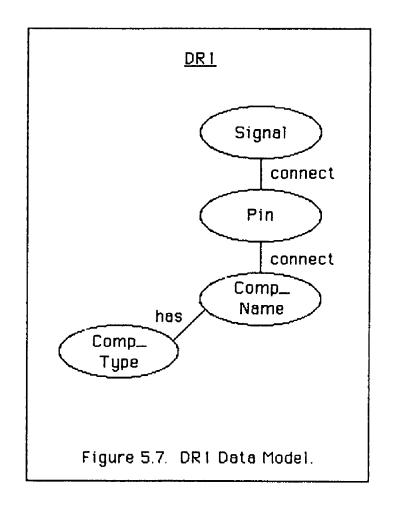

| Figure 5.7. DR1 Data Model.                                             |

| Figure 5.8. Target Output Rules for DR2 (dr2out.rul)                    |

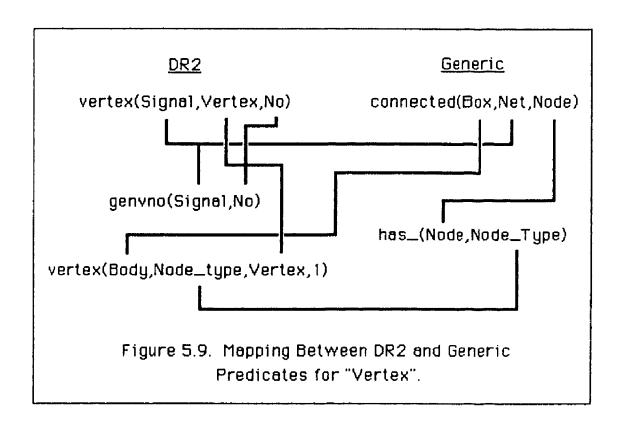

| Figure 5.9. Mapping Between DR2 and Generic Predicates for              |

| Figure 5.10 Target DBIF for DR2.                                        |

| Figure 5.11. Kept Data from the Generic to DR2 Translation              |

| Figure 5.12. Source TDL File in Native Format.                          |

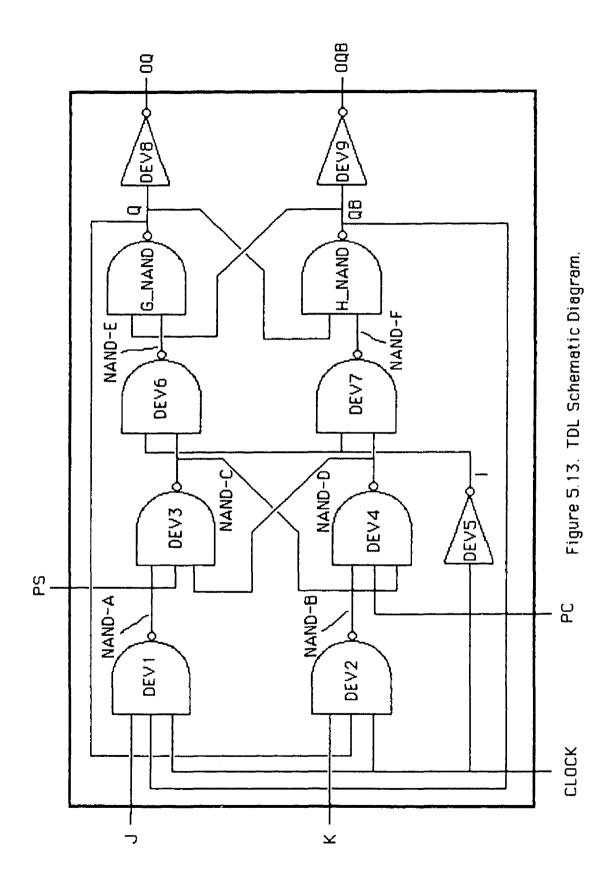

| Figure 5.13. TDL Schematic Diagram.                                     |

| Figure 5.14. Source TDL DBIF.                                           |

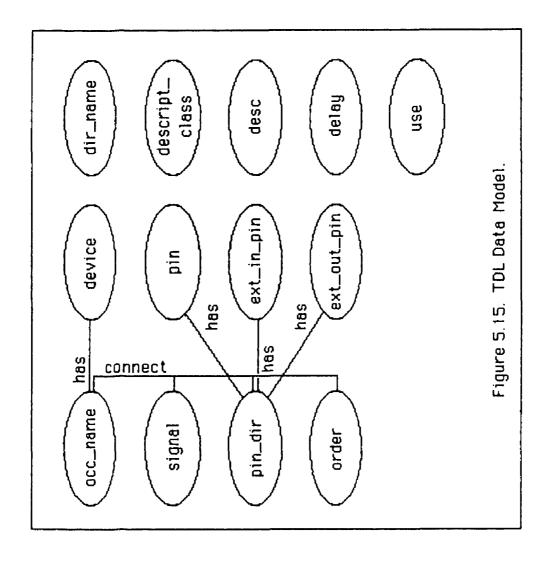

| Figure 5.15. TDL Data Model.                                            |

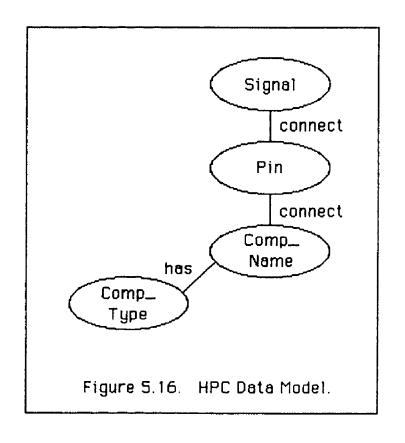

| Figure 5.16. HPC Data Model.                                            |

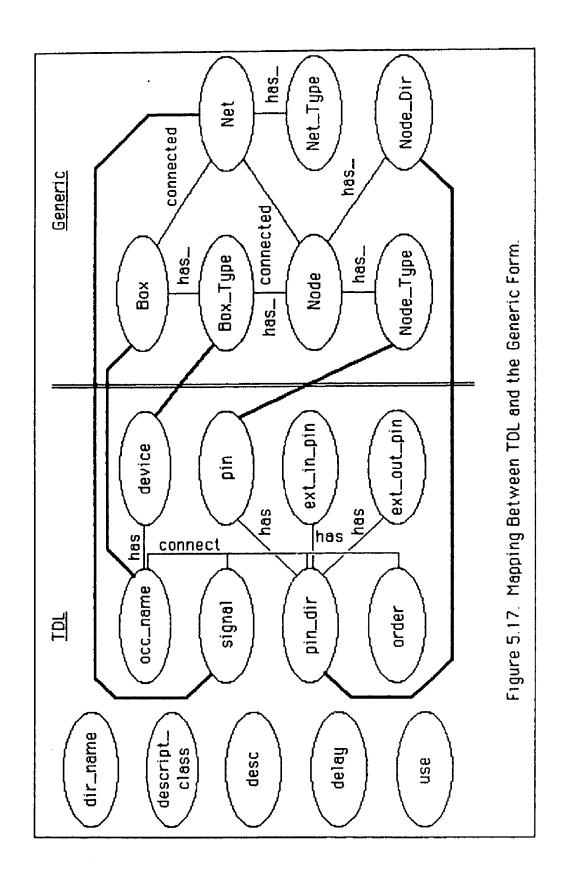

| Figure 5.17. Mapping Between TDL and the Generic Form                   |

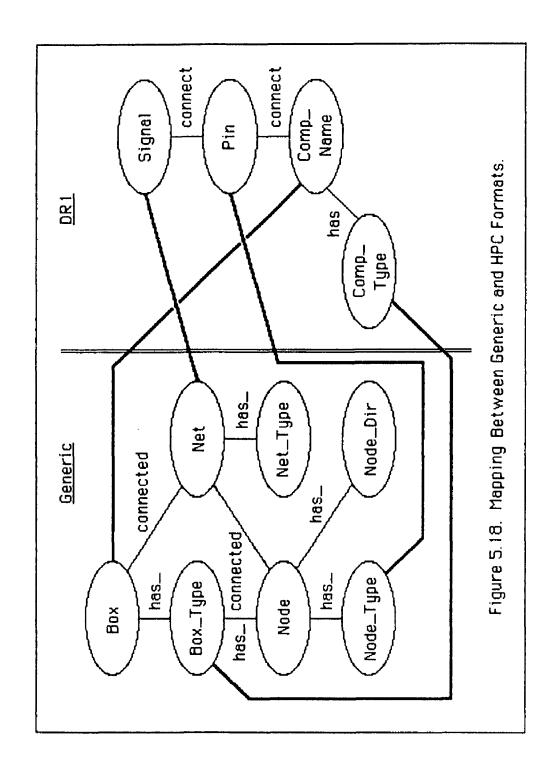

| Figure 5.18. Mapping Between Generic and HPC Formats                    |

| Figure 5.19. TDL Source Input Rules.                                    |

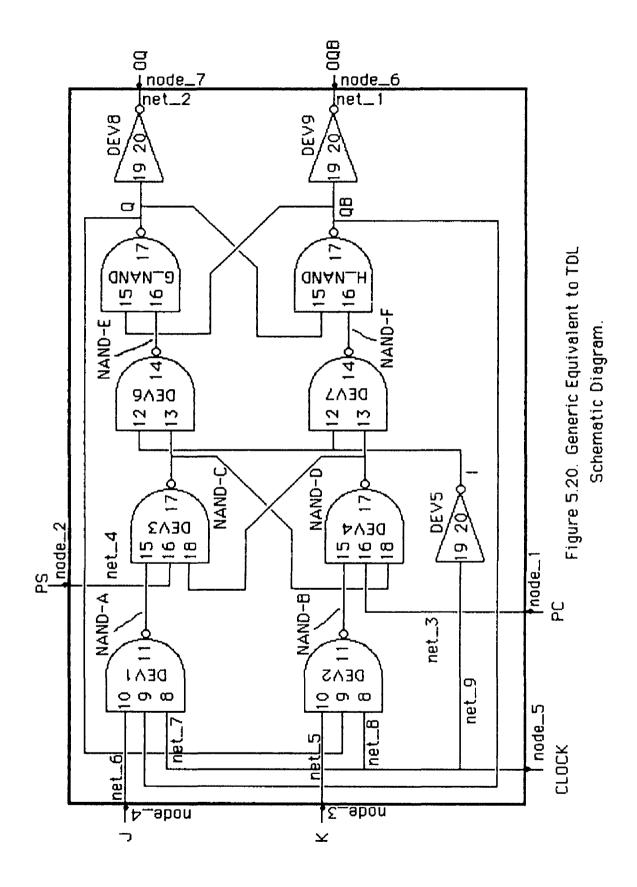

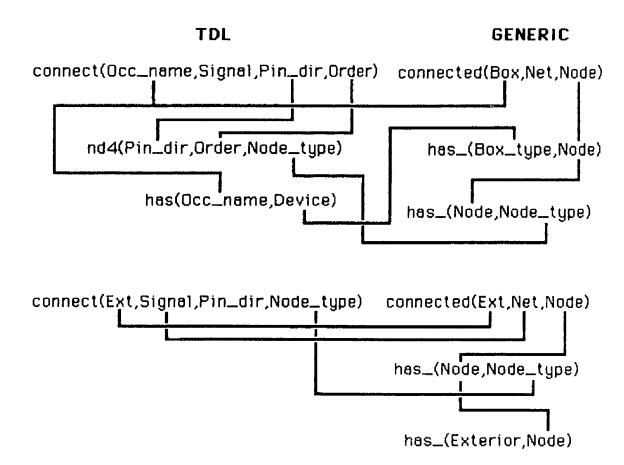

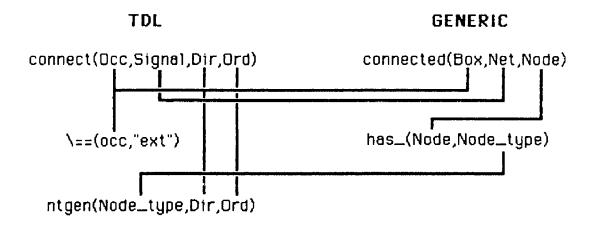

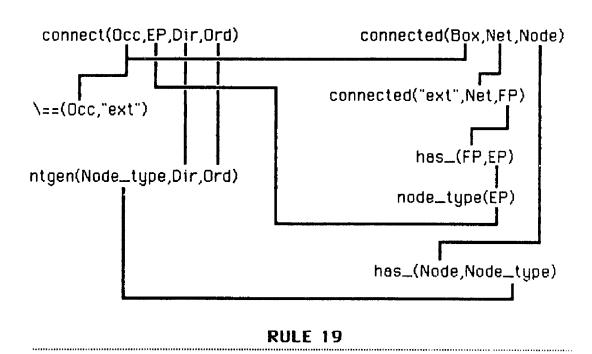

| Figure 5.20. Generic Equivalent to TDL Schematic Diagram                |

| Figure 5.21. Form.           | Rules for Connected in Translating TDL into Generic      |

|------------------------------|----------------------------------------------------------|

| Figure 5.22.                 | Target Output Rules for TDL.                             |

| Figure 5.23.                 | Connect Rules from the TDL Target Output Rules           |

|                              | Prototype System Log for Forward Translation (TDL        |

| Figure 5.25.                 | TDL and Generic Kept Facts.                              |

| Figure 5.26.                 | Target HPC (DR1) DBIF                                    |

|                              | Prototype System Log for Reverse Translation (DR1 to     |

| Figure 5.28.<br>Translation. | Target TDL DBIF Produced by the Reverse                  |

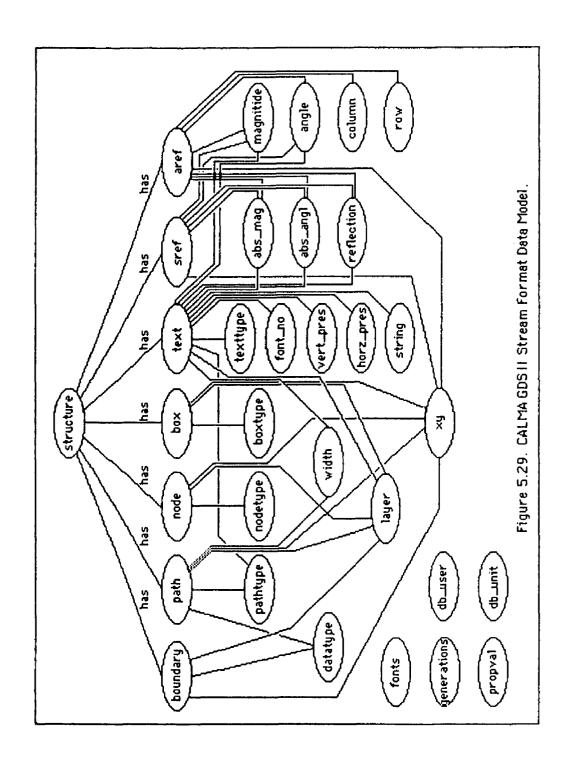

| Figure 5.29.                 | CALMA GDS II Stream Format Data Model                    |

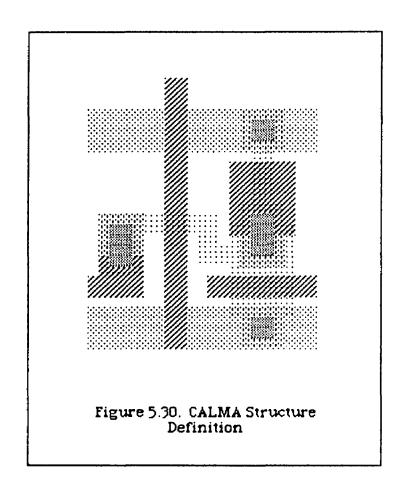

| Figure 5.29.                 | CALMA Structure Definition.                              |

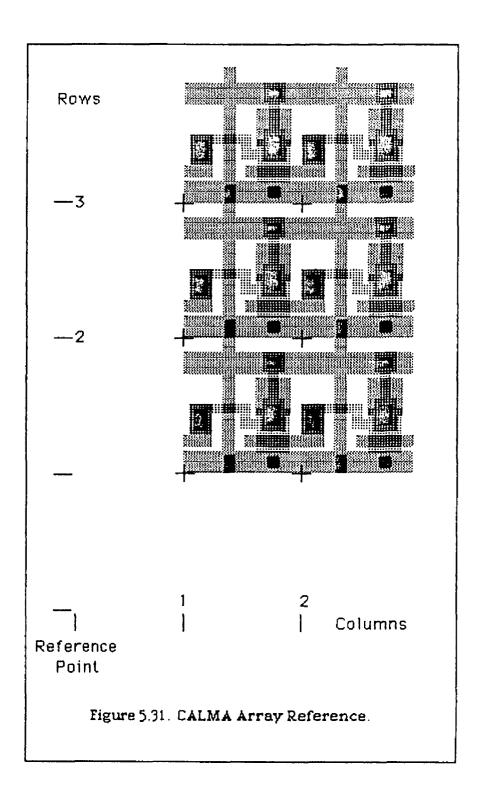

| Figure 5.31.                 | CALMA Array Reference.                                   |

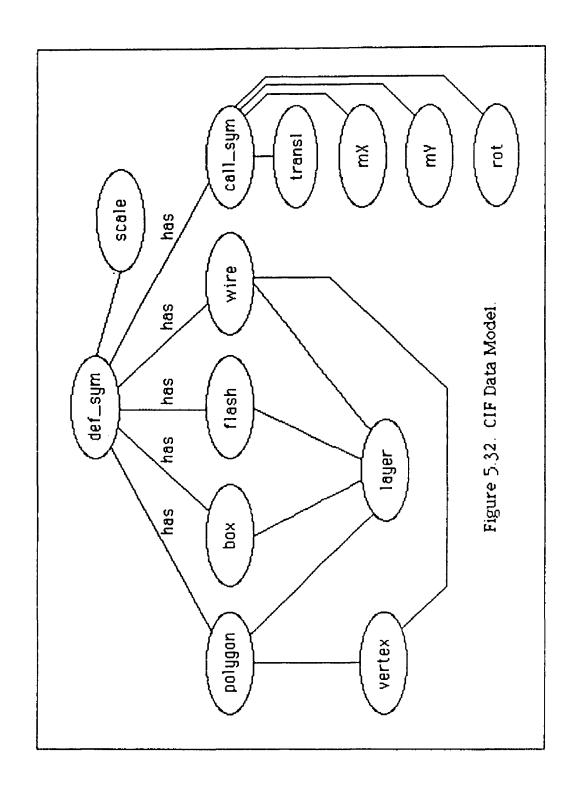

| Figure 5.32.                 | CIF Data Model                                           |

| F' ;ure 5.33.                | Mapping from CALMA to Generic Predicates                 |

|                              | Angular Rotation and Reflection Applied to a CALMA ence. |

| Figure 5.35.                 | Mapping from Generic to CIF Predicates                   |

| Figure 5.36.                 | Octagonal Approximation of a CIF Flash                   |

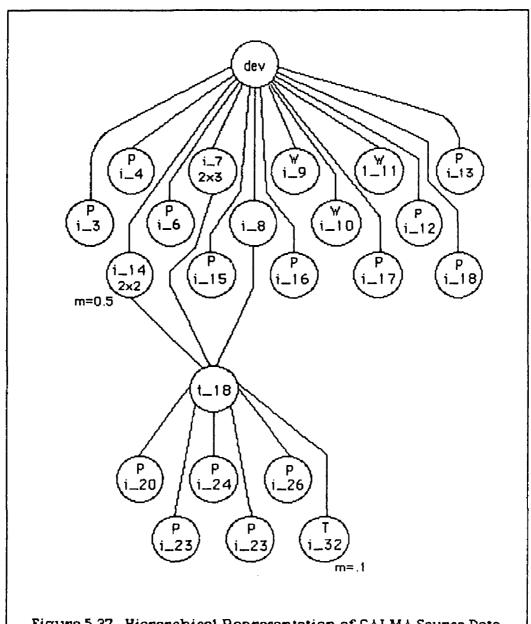

| Figure 5.37.                 | Hierarchical Representation of CALMA Source Data.        |

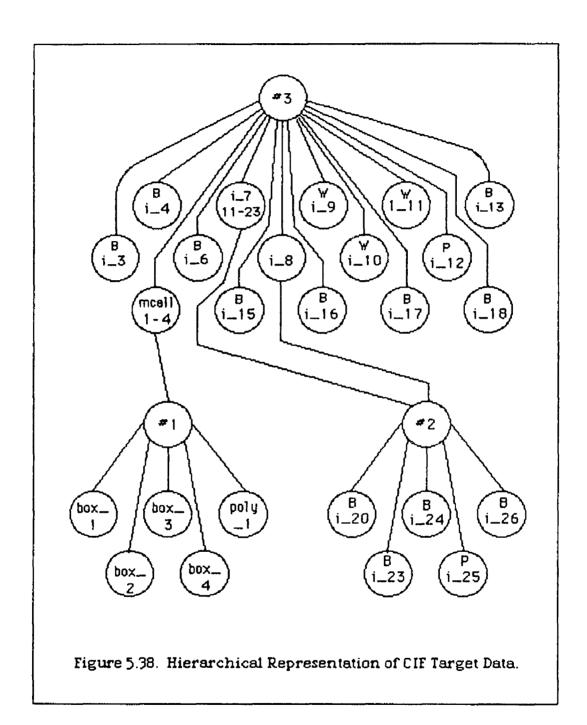

| Figure 5.38.                 | Hierarchical Representation of CIF Target Data           |

| Figure 5.39.<br>CIF)         | System Log for the Forward Translation (CALMA to         |

|                              | Kept Facts Generated in Translating CALMA into           |

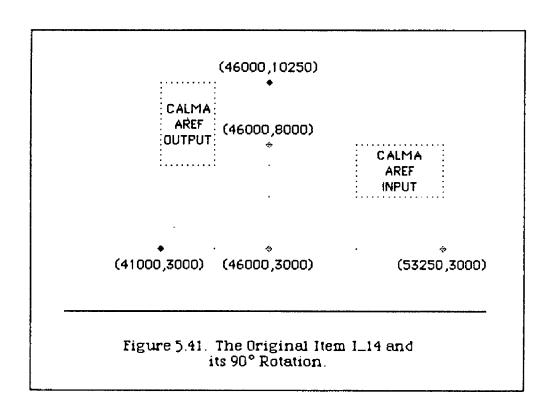

| Figure 5.41.                 | The Original Item I_14 and its 90° Rotation              |

| Figure B.1.                  | Original DR2 Representation as a Relation                |

#### ACKNOWLEDGEMENTS

There can be no doubt that a doctoral dissertation is the result of more than the work of the degree recipient. I, for one, recognize this and would like to acknowledge the contributions of those who helped me.

I am most grateful to Prof. Michel Melkanoff for his time, interest, support, and encouragement over the many years that I have been his student. No doubt this work wouldn't have been completed were it not for his contribution. I found his advice during the course of the research to be indispensable. He was always quite patient and a very good listener. Throughout the development of the concepts and the prototype, he reinforced the significance of the research, and this was a strong motivating factor in my persevering to the end. I especially appreciated his counsel on the editing of the dissertation, during the final days of its preparation.

I also found the comments and encouragement of the other doctoral committee members to be quite helpful. Many of their suggestions were incorporated into the approach taken in the research. In particular, Prof. Bussell suggested, back in 1981, that I consider a knowledge-based approach to solving this problem. That suggestion had a dramatic effect on the outcome of this research.

There have been many in the UCLA School of Engineering and Applied Science who have assisted me over the years with the administrative matters of graduate study. Special thanks to Brenda Ramsey, Verra Morgan, Rosetta Lindsey, Jamie Brodie, and Rosemarie Murphy for their help. Also, I would like to acknowledge the fine work of Doris Sublette in organizing and maintaining the holdings of our Computer Science Archives.

Also, Marilyn Caro assisted in developing part of the methodology. She built some of the formatters and compilers which were actually used to construct some of the test cases.

There were many people at Hughes Aircraft Company, Radar Systems Group, who gave me the opportunity to do this work. Furthermore, specific individuals shared their insights into this problem and to related issues. I am grateful for their technical contributions. Specifically, I would like to acknowledge Gloria Wilson and Grace Chen-Ellis for their assistance. Above all, I acknowledge the outstanding support of Abe Ansari, my department manager at Hughes. Not only did he share his many years of technical experience as a pioneer in the field of electronic CAD/CAM, but he made it possible for me to continue my studies while working. Were it not for he and the Hughes fellowship program, I would not have been able to pursue this degree.

Both Addison-Wesley and the Calma Company should be acknowledged for their support of academic research. Both granted permission for me to use their copyrighted material as noted in the body of this text.

Lest we forget the importance of computers in our research, I must thank our systems managers and programmers for their assistance. The last year of research was performed using Prolog on the UCLA Center for Experimental Computer Science. I am most appreciative of the outstanding support by Dr. Terry Gray and his staff of the Center. Specifically, Doris McClure and Anne Finestone were quite helpful in assisting me with disk space and in answering system questions. At Hughes, Mike Kimura was quite helpful with the VAX VMS system and in getting me linked to UCLA via phone line.

Pursuing this degree was quite a burden on my family. Words cannot express the sacrifices made by my wife, Denise. She took care of the children, ran the household, and tried to keep order amidst the chaos. Even still, she had time and energy to encourage and reassure me and to share in the excitement when I would make a big break-through in this work. I will be eternally grateful for all of her hard work. Also, a special thanks to Liz and Rex Harris and Marge Fisher who often cared for the children when Denise and I were busy and needed help.

Finally, and most important, I acknowledge that were it not for God paving the way and giving me the strength, this work would never have been possible. Truly, it was a miracle that many of the obstacles were overcome. I shall be thankful to Him all of the days of my life.

#### **VITA**

- June 3, 1951 Born, San Diego, California.

- 1972 B.A., Mathematics-Computer Science, University of California, Los Angeles

- 1972-1975 Teaching Associate, Department of Computer Science, University of California, Los Angeles

- 1975 M.S., Computer Science, University of California, Los Angeles

- 1975-1977 Member of the Technical Staff, Technology Service Corporation, Santa Monica, California

- 1977-1978 Senior Scientific Programmer, ITT Gilfillan, Van Nuys, California

- 1978- CAE/CAD Systems Development at Hughes Aircraft Company, Radar Systems Group, El Segundo, California.

- Head, CAD Systems Engineering Section,

Radar Design Automation Laboratory,

Hughes Aircraft Company.

#### **PUBLICATIONS**

Hooper, Richard P., "Artificial Pattern Generation," Proceedings of the Conference on Computer Graphics, Pattern Recognition. and Data Structures, May 14-16, 1975, with A. Klinger.

#### ABSTRACT OF THE DISSERTATION

An Application of Knowledge-Based Systems to Electronic Computer-Aided Engineering, Design, and Manufacturing Data Base Transport

by

Richard Preston Hooper

Doctor of Philosophy in Computer Science

University of California, Los Angeles, 1985

Professor Michel A. Melkanoff, Chair

The proliferation of computer-aided engineering (CAE), design (CAD) and manufacturing (CAM) systems for electronic design has created a excess of CAE/CAD/CAM database formats. These databases vary from one system to the next, and yet they often carry common information, represented in different formats. In spite of this variation, databases must be transported between systems, since electronic design requires the use of features from several CAE/CAD/CAM systems.

The significance of this work is underscored by other attempts to define a transport method. Most notable is the IGES (Initial Graphics Exchange Specification) standard. Thus far, there are shortcomings with these methods. The IGES standard was primarily developed to handle CAE/CAD/CAM data used to describe mechanical designs not electronic designs. Consequently, IGES does not address all of the data elements of electronic CAE/CAD/CAM systems.

Commercial offerings which translate between CAE/CAD/CAM formats do not translate all of the data. This is because there is usually some data which is unique to each system and cannot be translated. Most commercial translators disregard this data. This is not satisfactory in all cases, since important data relationships are lost in translation.

This dissertation defines a methodology for the transport of data-bases between independent CAE/CAD/CAM systems. In order to demonstrate the feasibility of this methodology, a prototype system was developed. A non-traditional, expert systems approach was used to solve the problems which have plagued earlier attempts at a data transport method. The prototype was implemented using PROLOG, running under LOCUS/UNIX on a VAX network. The research has been limited in scope to CAE/CAD/CAM systems used for the development of electronic systems as opposed to mechanical systems.

The conclusion of this research is that a this approach can be used to provide a method for transporting data between distinct CAE/CAD/CAM system types. The prototype translation algorithm is driven by knowledge bases which describe the CAE/CAD/CAM data for-

mats and semantics. New systems can be added to the knowledge base with a relatively minor amount of effort.

## CHAPTER 1 INTRODUCTION

The purpose of this dissertation is to develop a methodology for transporting data bases of differing form, schema, and content between distinct types of systems for computer-aided engineering (CAE), design (CAD), and manufacturing (CAM). The focus of this work is in the electronic design field in contrast with other fields (e.g., mechanical design). The dissertation describes electronic CAE/CAD/CAM and the requirement for data transport, defines a data transport methodology, presents a prototype system, and analyzes the application of the prototype to several test cases.

#### Background

The need for increased productivity through the automation of electronic systems development has brought about rapid development of CAE/CAD/CAM systems. Several companies have developed commercial systems providing one or more CAE/CAD/CAM functions for the development of digital/analog circuits, printed circuit boards, and VLSI chips. New systems are constantly becoming available.

Since CAE/CAD/CAM provides a highly competitive market, most companies are worked independently, often without regard for the prob-

lem of interfacing their system with other systems. However, the complete cycle of electronic system development requires that features of several systems be used. No system provides all features necessary for the design, implementation, and fabrication of an electronic system. Several CAE/CAD/CAM functions are necessary, including

- graphics/drafting,

- design capture,

- analysis/simulation,

- placement/route,

- layout and artwork generation, and

- manufacturing aids generation.

Usually these functions will reside on several different computer systems.

Without the benefit of a method for automatically transporting data between systems in order to use each function, the only alternative is to manually re-encode the data necessary to drive each CAE/CAD/CAM system. This approach is expensive since the data must be verified each time the encoding process is repeated. This approach also results in unnecessary delay which defeats a major purpose behind the use of CAE/CAD/CAM. Consequently, there is a strong motivation to translate databases between systems, automatically.

Another motivation for database transport between CAE/CAD/CAM systems is to set up libraries of common data (e.g., graphic symbol libraries). Once established, a single library can be shared by different vendor systems providing that some data translation method is available. Maintenance of libraries is thus reduced by only requiring the update of a single common library.

However, since each brand of CAE/CAD/CAM system utilizes a different database schema/organization, there has been no direct, general data mapping approach available. Typically, specific point-to-point translators are developed by users as needed. The difficulty with this approach is that when the source and/or target data formats are revised by the system developers, the translators must be rewritten. Also, it is difficult to integrate new systems into a distributed CAE/CAD/CAM system network, since translators must be written to move data between the new system and each other system with which it interfaces.

#### Goal

An alternative data transport methodology is the goal of this doctoral research. The research began about six years ago, motivated by the requirement for data transport within the CAD environment at the Radar Systems Group (RSG) of Hughes Aircraft Company. By investigating the flow of information from the inception of an electronic design to its fabrication, it was clear that several CAE/CAD/CAM systems were required, and that the individual data bases of these systems were unique in both form and content. Six years ago at RSG, there were a few Computervision stations, two CALMA's, a DECsystem-10 (running Hughes-developed CAD

software), and a Hughes schematic capture (graphics) system. At that time, data was not easily transported between systems. For example, data entered on the Hughes schematic capture system was used to facilitate changes to the drawing and subsequent re-draw. Once the design was final, the drawing was released. In order to get a schematic database onto the DECsystem-10 CAD system, the data on the schematic drawing was re-encoded for data entry directly onto the DECsystem-10.

In the years which followed up to the present, this requirement remains. CAE/CAD/CAM technology has undergone many improvements, but the need for a data transport methodology has not been eliminated. The same CAD organization at Hughes RSG has grown and in addition to the systems available six years ago, there are more CV's, more CALMA's, two DECsystem-20's (the DECsystem-10 was converted), two VAX's (running VLSI/VHSIC CAD system), 16 VALID Logic Workstations, and two DAISY systems. Because the number of distinct types of CAE/CAD systems has increased, the data transport problem has become more complex. Attempts at identifying standards within classes of CAE/CAD/CAM data (e.g., schematic, layout, artwork) have succeeded on a limited basis.

Indeed, within the last five years there has been an effort to establish an international CAD data standard, "Initial Graphics Exchange Specification (IGES)." This standard has developed slowly and the major emphasis has been on graphics information and the mechanical CAE/CAD/CAM application. Finally, in 1980, version 1.0 of this standard was accepted and released as an ANSI standard. The intent of the standard is that all systems will provide interfaces to and from their internal

formats into the IGES format. There is no date yet projected for when this might be feasible. Also, there is uncertainty as to whether all commercial systems will adhere to this standard for economic reasons. The emergence of alternative CAD data standards add to the uncertainty.

This year, a new format was introduced for CAE/CAD/CAM data transport. As yet, version 1.0 of this Engineering Design Interchange Format (EDIF) has not been formally released. The inclusion of EDIF in this dissertation occurred recently. The contribution of this potential standard as described in its preliminary release will still not address many of the problems described in Chapter 3. However, as new standards arise, they may add to the growing superset of all data entities which describe electronic designs.

This dissertation will attempt to further clarify the problems of CAE/CAD/CAM data transport, define a solution to the problems, and describe a prototype which demonstrates the feasibility of the concepts developed. To begin with, the CAE/CAD/CAM environment is described in Chapter 2. This includes a description of how data flows between CAE/CAD/CAM processes in both microelectronics (chip) design and printed circuit board design. The categories of this data and differences in its representation between systems are presented. This chapter concludes with a review of existing standards for CAE/CAD/CAM data exchange.

Chapter 3 defines the proposed data transport methodology. First, the difficulties in transporting data between systems are described. Then, the general approach to overcoming the difficulties is presented. Finally, a systems architecture is defined.

Chapter 4 describes the prototype system. The proposed system has been implemented using PROLOG. This chapter contains a brief introduction to PROLOG, a description of the PROLOG programs used to prototype the proposed system, and an explanation of how the prototype operates.

Chapter 5 describes several test cases which demonstrate the feasibility of the prototype. One case is the transport of a hypothetical schematic data base into another, different hypothetical format. The second case involves translating an actual schematic data base (TEGAS description language - a.k.a. TDL) into a Hughes PCB CAD data base format. In this second case, not only is the data base translation demonstrated, but also, a compiler was written and is presented to demonstrate the feasibility of translating an arbitrary CAE/CAD/CAM data language into a generic format. Finally, a third example, two widely recognized, but distinct data formats used for VLSI layout description (CALMA Stream Format and CalTech Intermediate Form) are transformed both ways.

Chapter 6 summarizes the work and states the conclusions which were drawn during the conduct of the experiments.

Appendix A contains a glossary of terms to aid the reader and to clarify the intent of the author.

Appendix B discusses an earlier prototype implementation approach which was attembpted using data base technology. This approach was subsequently abandoned due to inherent problems with translation rule representation. This decision led to the use of a knowledge-based systems

approach using Prolog.

Appendices C through G show sample CAE/CAD data bases which were used as test cases for the prototype described in Chapter 4.

Appendix H shows an excerpt of the syntax for the TEGAS Design Language (TDL). The excerpt is included so that the TDL sample of Chapter 4 can be better understood.

Appendices I, J, and K provide a data base and rules used as inputs in a CALMA to CIF test case described in Chapter 5.

Finally, Appendices L, M, N, O, P, Q, and R provide the various outputs from the prototype implementation for the CALMA to CIF test case.

# CHAPTER 2 CAE/CAD/CAM ENVIRONMENT

To illustrate the data transport problem, consider a representative CAE/CAD/CAM environment for electronic design. The design process consists of several stages of definition, simulation, analysis, and mechanization until the design goal is reached. The process is iterative and CAE/CAD/CAM tools are utilized at all stages of this design process to perform computationally complex tasks, improve the quality and reliability of the design, and to verify consistency between the various stages of design. Each CAE/CAD/CAM tool/system has unique data input/output formats. A more in-depth look at the electronic design process, the CAE/CAD/CAM tools, the data used by the tools, and data standards will make this more apparent.

The first step in the electronic design process is the conceptual design of the system. This is a top-level definition which identifies the major functions to be performed by the system. All of the requirements are allocated to one of the various functions. System performance parameters are related to the functions which affect their outcome. Conforming to performance requirements and environmental considerations, the selection of electronic circuit technology will be made (e.g., TTL, Shottky, ECL, CMOS, Custom VLSI, Gate Array, etc.) and the physical packaging will be

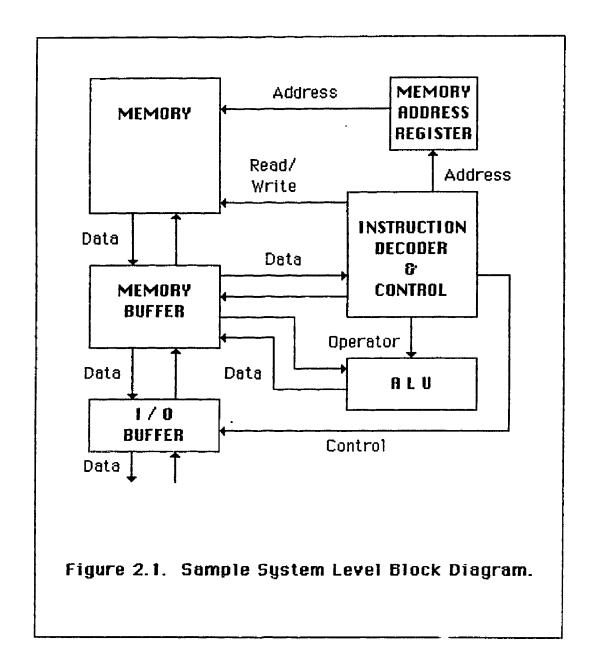

established. Once the functional specification is established, each function is defined in terms of processes to be performed, inputs, outputs, and the functions with which they interface. Usually this relationship is illustrated with a system-level block diagram. Figure 2.1 shows an example of a block diagram for a hypothetical computer system. This conceptual definition of the system and top-level functional decomposition is generally performed without the use of a CAE system, although several computer simulations and other analyses are used.

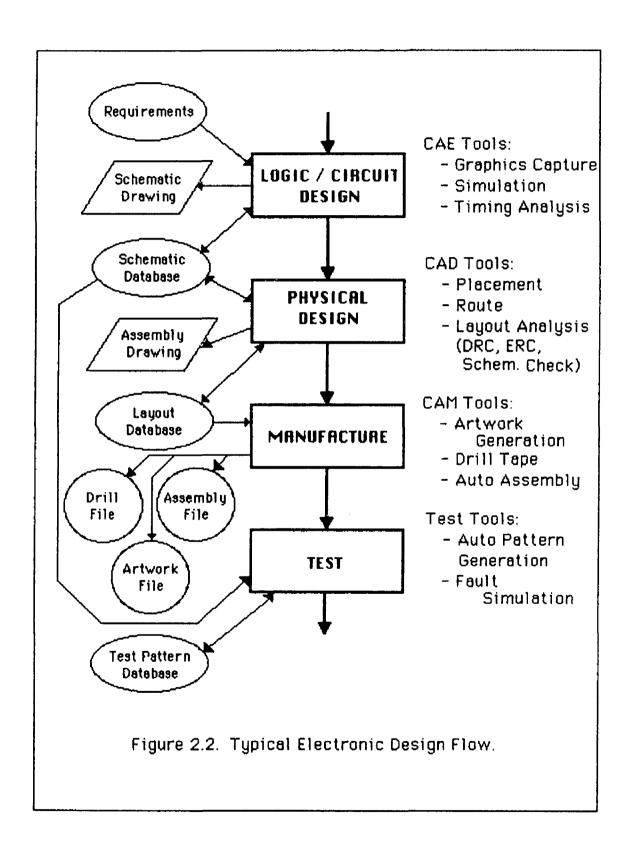

Each system function to be performed is sufficiently described so that the next level of detail can be defined. In the case of the hypothetical computer system (Figure 2.1), the next step of refinement might break down the "Instruction Decoder & Control" into sub-functions. Refinement and functional decomposition continue until a level is reached which can be implemented on a standard physical device such as a gate array, custom wafer, or a printed circuit board (PCB). At this point, the development of the device begins. The development flow consists of the several steps shown in Figure 2.2: logic/circuit design, physical design, manufacture, and test.

#### 2.1 Custom VLSI or Gate Array

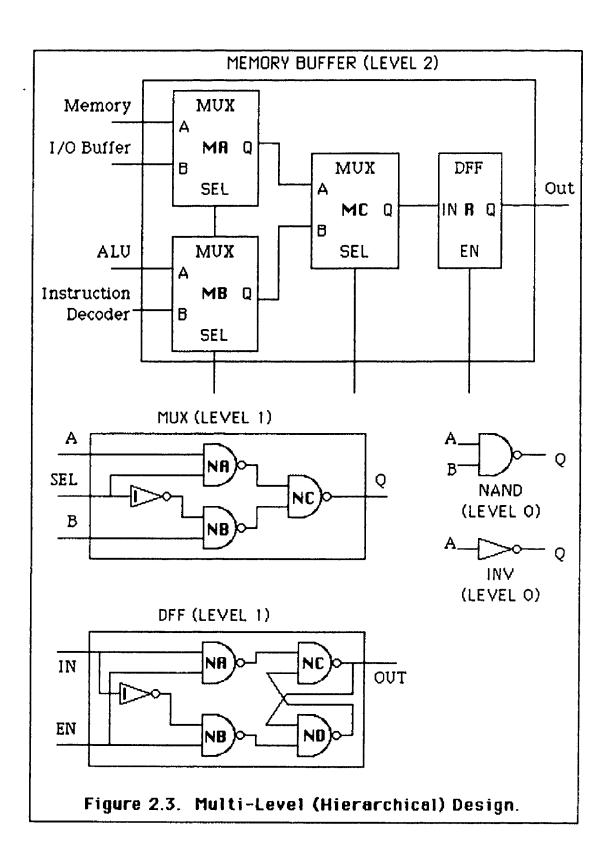

When a logic function is to be implemented into a gate array or custom VLSI chip, the design may have several levels of hierarchy. The lowest level refers to primitive cells (macros). These are implemented using analog devices which are built into the semiconductor medium. This hierarchical design style is shown in Figure 2.3. In this example the functions "NAND" and "INV" are primitive cells.

Typically, when a gate array or custom VLSI design begins, a library of standard primitive cells is formed from basic logic functions as those in the preceding example ("NAND" & "INV"). In some cases, the primitives may be quite intricate, utilizing > 100 transistors. These standard primitives are analog designs whose functions can be verified by a circuit simulator. This simulation will verify the proper voltage levels, voltage transitions, and timing. At the end of this activity, the library of primitive cells will be available as a foundation upon which logic design will be built. The circuit simulation will also generate the necessary data to formulate logic models for higher level logic simulations, working with digital (Boolean) signals rather than analog simulations.

Once the primitive cell library is available, attention turns back to the top-level block diagram. Each function at this level is decomposed into sub-functions, and these sub-functions are sub-divided again. This functional decomposition repeats until the primitive cell level is reached. Once a sub-function can be expressed in terms of primitive cells which have logic simulation models, the sub-function can be verified using a logic simulator.

As sub-functions are simulated and verified, they can be combined to form larger functions. The larger functions can then be verified by simulation. This process is repeated until the entire gate array or custom VLSI device is verified.

In conjunction with logic simulation, timing verification is used at each level in the hierarchy. The signal propagation delays are computed using timing models for all cells and the signal media itself. A network analysis of these propagation delays will verify that signals arrive at the

proper time at the various nodes in the path.

When the gate array or custom VLSI device has a completed logic design which has been verified, then the logic design must be mechanized into interconnected physical cells within a wafer geometry. The CAD tools identified in Figure 2.2 are used to achieve this. First, the primitive cells are placed according to routability criteria, taking into consideration any thermal restrictions and/or timing constraints. Cell placement can be accomplished either manually or semi-automatically.

With the cells placed, signal routing proceeds. Using the available conductor layers in a gate array or custom VLSI device, paths are selected according to the routing algorithm deployed. After automatic routing is finished, there are often signals for which a path could not be found by the router. These "route fails" must be resolved by ripping up routed lines, and manually re-routing the "route fails" and any ripped-up lines. After manual re-route, a design rule check is performed to determine if any geometric spacing constraints, imposed by the circuit and process technology (e.g., CMOS), have been violated. Electrical rules must also be checked to determine layout correctness with regard to electrical parameters, such as loading. Another check performed after any re-routes is a schematic check. This verifies that all signals in the logic design have a physical counterpart in the layout. Once the layout passes all of the post-route checks, a pattern generator tape is produced. This tape is used to guide the various steps in the fabrication process.

When all of the gate-array and custom VLSI devices have been designed and fabricated, they can be combined to construct a printed circuit board, implementing still a larger scale function.

2.2 Printed Circuit Boards In the case of a PC board implementation, this level of functional decomposition constitutes the first level above the components which have been selected by the circuit technology decision at the conceptual design step. Examples of components might be logic elements (e.g., NAND gates, counters, and registers), integrated circuit chips (IC's), or discrete analog parts (e.g., resistors, transistors, capacitors, etc.).

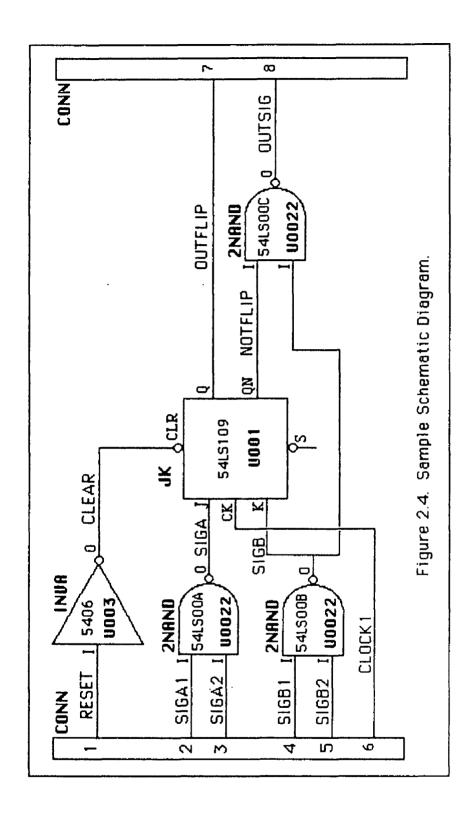

Each PC board is finally defined in sufficient detail so that a completed design can be carried through to fabrication. The PC board is documented in terms of a block diagram showing subfunctional areas (i.e., macros). As the PC board is refined, various subfunctions are designed using components from the set of the selected circuit technology. During this refinement a logic schematic is developed, detailing all of the logical elements and how they are interconnected to perform the specified function (see Figure 2.4).

As portions of the logic are defined, simulation is performed to insure the proper logic functioning of the design before it is implemented using actual components. Timing analysis is performed to insure that there were no incorrect assumptions made about the delays in signal propagation through various logic elements or errors in clocking. Signal loading and drive capacity are also checked to insure compliance with electrical rules. Any problems detected are corrected before the logic design is released for physical design.

When the PCB design activity is completed, each logic element is assigned to a physical component or chip. In small scale integrated circuitry, chips often contain multiple logic elements of the same type (e.g., 4 NAND gates). After the assignment of logic elements to components, the components are located on the PC board. At this time the placement is analyzed before signal routing to insure correct thermal distribution over the PC board. Once the design passes these validation tests, the next step is to route the interconnections between components upon the remaining PC board area not taken up by components and other obstacles. After route, a final analysis is performed to determine if the paths chosen violate signal length requirements thus causing timing problems or whether there is too much parallelism among adjacent signals to constitute inductive noise problems. Assuming the selected route paths pass these critical tests, the design is complete and ready for manufacture.

Manufacturing consists of etching and drilling the printed circuit boards, generating continuity tests for the etched board, inserting components upon the board, soldering the components in place, and wiring the backplane which contains slots for the individual printed circuit boards. In addition to these processes associated just with the electronic aspects of the design, there are many other fabrication processes necessary to assemble all of the mechanical parts into a final system.

The use of CAE/CAD/CAM tools has had a significant impact on this overall design process. Figure 2.2 shows where data bases and automated tools are used to assist in the electronic design.

## 2.3 CAE/CAD/CAM Tools

The intent of CAE/CAD/CAM is to off-load any processes which do not require human judgement and experience onto automated processes, i.e., to effectively utilize man and machine resources. Automation is applied to the design and manufacturing cycle in several areas. Figure 2.5 lists several CAE/CAD/CAM functional areas with examples of tools in each area.

Logic Design Aids. From the time a designer receives a requirement specification until a prototype is developed, logic design aids facilitate decision making. To begin with, graphics editors allow a designer to enter, edit and display his evolving logic schematic. As the design proceeds, design aids software indicates any deviation from standards and warns the designer about potential logic errors, producibility problems, and testing difficulties. This feedback speeds up the development cycle by calling to the attention of the designer details that he might have discovered at a less opportune time during development.

Logic simulators and test pattern generators can also be used incrementally as a designer adds more of his logic to the emerging design. These tools help the designer evaluate trade-offs and select the best of design alternatives. In general, the designer gains confidence in his design because the tools identify logic errors and measure how easily the design can be tested once fabricated.

Analysis Tools. Along with logic design aids, analysis tools also raise confidence that the design is correct and will function properly once it is

# Logic Design Aids

- . Graphic (Schematic) Editor

- . Logic Simulator

- . Test Case Generator

# Analysis Tools

- . Thermal Analysis

- . Propagation Delay & Timing Analysis

- . Noise Margin Analysis

- . Loading Analysis

# Physical Design Aids

- . Routing

- . Gate Assignment

- . Component Placement

- . Design Rule Checks

- . Post Route Analysis -Line Lengths, Signal Parallel Runs

## Drawings & Reports

- . Assembly Drawings

- . Schematic Drawings

- . Pin/Signal Lists

- . Parts Lists

- . Test Case Data

# Manufacturing Aids

- . Numerical Control Machinery Data -Drill, Auto Component Insertion

- . LSI Mask File

- . PCB Artwork File

## Libraries/Data Bases

- . Graphics Capture

- . Logic Design (Schematic) Data Base

- . Configuration Management Status

- . Standard Components/ Parts Layout Library

- . Layout/Route Data Base

- . LSI Macro Cell Library

- . Drawing Symbol Library . Simulation/Timing

- Models Library

- . Component Packages Library

Figure 2.5. CAE/CAD/CAM Data Functions.

implemented into a physical design. For example, loading analysis will indicate whether there are too many components being driven from a single signal source. Analysis of the physical design before fabrication will often prevent costly errors. For example, once components have been placed on a printed circuit board (PCB), a thermal analysis will indicate whether overheating is likely to occur from the placement of too many "hot" parts in close proximity of one another.

Physical Design Aids. Once the logic design is complete, the mechanical, geometrical, and other non-electrical constraints must be used to determine how to implement the design. The steps involved include placement and route. Once standards for board/wafer geometry and thermal requirements are established and defined in libraries, placement and route can proceed automatically, driven by the logic design data base and a few directives which define router strategies and priorities to be considered during these processes.

Drawing/Report Generation. The output of CAE/CAD/CAM processes is typically a report or a drawing. Following the schematic capture, a pin/signal report is written which contains all of the information pertaining to which components are interconnected. A schematic drawing is the best format to display and verify the logic design data following design capture. The designer can make design changes to the schematic and have a clean drawing produced with the new changes reflected. An assembly drawing can be generated automatically once the components have been placed. This can be used by manufacturing planners to provide instructions on how to build a PC board. In general, CAE/CAD/CAM

processes create, use, and update design data which is then presented in the form of drawings or reports.

Libraries/Data Bases The CAE/CAD/CAM processes require a large volume of data in order to describe the designs under development. Libraries of standard parts or cells and board/wafer geometries are maintained to minimize the amount of data that must be re-entered each time a new design is created. Libraries are created for simulation and timing models, drawing symbols, cell layout patterns, component package specifications, and component artwork (footprint) patterns. These libraries minimize errors and insure consistency, where necessary, from one design to the next.

A design data base is created for each design. This contains data such as the logic network, assignment of logic gates to physical components/cells, placement locations, and signal routing. The data base contains references to standard library parts/cells, board/wafer geometries, and the interconnection of parts. While the collection of data describing a design is referred to as a data base, the data actually may reside in a variety of files and data bases depending upon the CAE/CAD/CAM system. Examples include those listed in Figure 2.5.

Because of the large number of parameters in the design data bases and libraries, changes in a design after its entry into a CAE/CAD/CAM system can have far reaching effects. For example, the decision to substitute parts in a design can affect several data bases. If a design has been released for manufacture, it means that a significant commitment has been made in time and money to the system configuration in which the design is

embedded. Still, changes are sometimes necessary after initial release and a method is necessary to keep track of which revision of one design is to be interfaced with other designs which together consitute a complete configuration. This is the role of a configuration management system, and some CAE/CAD/CAM systems provide this facility.

Manufacturing Aids. Once the design is complete and the physical implementation routines have obtained a feasible mapping of logic into components and interconnections within the established constraints, manufacturing aids are generated from the design data base. Computer-aided manufacturing relies on these tools to improve the throughput of the factory much the same way CAD tools improve the productivity of engineers. Examples of manufacturing aids include photo-plotter tapes for artwork generation/PCB etch, automatic assembly files, continuity check tapes, and drill tapes. Each of these aids represents a final output derived from the various CAE/CAD/CAM data elements describing the equipment to be built.

#### 2.4 CAE/CAD/CAM Data for Electronic Design

CAE/CAD/CAM data for electronic equipment, such as a radar signal processor, can be broken into several categories of information: logical, physical, electrical, thermal, and timing. In each category, the data type may be textual, numeric, graphic, or special-purpose. Each data type may have several variations such as floating-point and integer numeric representations. Figure 2.6 lists the data categories, and examples of information in each category. Usually the format of a specific category of data varies from one CAE/CAD/CAM system to the next. There are numerous

#### LOGICAL

- . Digital/Analog Function

- . Schematic Drawing . Graphic Symbols

- . Logic/Circuit Network

## PHYSICAL

- . Component Size

- . Pin Description

- . Board/Wafer Geometry . Assembly Drawing

- . Pin/Signal Data

## ELECTRICAL

- . Power Consumption

- . Loading

#### THERMAL

. Heat Dissipation

# **TIMING**

- . Rise/Fall Times

- . Clock Cycle

- . Set-up/Hold Times

Figure 2.6. CAE/CAD/CAM Data Categories.

approaches to establishing a structure for CAE/CAD/CAM data bases. Many of these have been documented, and are referenced here as background. [Ciam76a, Ciam76b, Gutt82, Hask82, Kawa78, Lacr81, Such79, Vall75, Wilm79, Wong79, TDL83, Mead80] At this time there are numerous commercial CAE/CAD/CAM systems, and each maintains a distinct data base format: CAE Systems, CALMA, Computervision, Daisy, Mentor Graphics, Silvar-Lisco, and Valid Logic to name a few.

It is precisely the wide variety of data formats which has created the problem of CAE/CAD/CAM data transport. Two cases demonstrate the problem.

Case 1. Consider a data base consisting of schematic interconnect information. A sample schematic diagram was shown in Figure 2.4. A data base representing this information describes how the component pins are connected logically. This data can be represented in a variety of ways and is referred to as "pin-signal data", "from-to data", and by other names which connote the data content.

One example of the format this data takes is provided by the Hughes DECsystem-20 CAD system [Wong79]. Here, interconnect data is contained within the "Build-Design" data base. The structure of this data is indicated in Figure 2.7.

Figure 2.8 shows the data content of the build-design data base for the sample shown in Figure 2.4. This data base represents a PCB design by describing the components, their pins, pin function, signal names, and other data used by a variety of CAE/CAD/CAM processes.

Another format for schematic interconnect data is that of an often used test system at Hughes Aircraft: the Hewlett-Packard (HP) DTS-70 system [HP80]. The syntax for this data is shown in Figure 2.9. This form is man/machine readable (ASCII) since it is also designed for direct manual output into the system. In order to reduce error and minimize time, a spe-

```

ATTRIBUTE SIGNAL ABBREV S TEXT KEYED COL 18

ATTRIBUTE FEED THRU ABBREV FT TEXT COL 9 9

ATTRIBUTE TEST POINT ABBREV TP TEXT COL 10 10

ATTRIBUTE CONNECTOR ABBREV CR TEXT COL 11 11

ATTRIBUTE COMPONENT NAME ABBREV CN TEXT

KEYED COL 12 15

ATTRIBUTE COMPONENT PIN ABBREV CP TEXT

KEYED COL 16 20

ATTRIBUTE PAGENUMBER1 ABBREV PN1 TEXT

COL 22 23

ATTRIBUTE PIN SWAP ABBREV PS TEXT COL 24 24

ATTRIBUTE SEQUENCE ABBREV SEQ TEXT COL 25 26

ATTRIBUTE CRÍTICALITY CODE ABBREV CC TEXT

KEYED COL 30 31

ATTRIBUTE ELEMENT PIN ABBREV EP TEXT

COL 32 32

ATTRIBUTE ELEMENT ADDRESS ABBREV EA TEXT

COL 33 34

ATTRIBUTE MULTIPLE SOURCE ABBREV MS TEXT

COL 35 35

ATTRIBUTE SOURCE ABBREV SR TEXT COL 36 36

ATTRIBUTE ELEMENT NAME ABBREV EN TEXT

KEYED COL 37 42

ATTRIBUTE ELEMENT TYPE ABBREV ET TEXT

KEYED COL 47 56

ATTRIBUTE LOAD ABBREV LD REAL COL 57 65

ATTRIBUTE PIN FUNCTION ABBREV PF TEXT

COL 66 70

ATTRIBUTE NO CONNECT ABBREV NC TEXT COL 71 71

ATTRIBUTE SIGNAL TYPE ABBREV ST TEXT COL 72 72

ATTRIBUTE COMPONENT TYPE ABBREV CT TEXT KEYED

COL 81 88

ATTRIBUTE PINQUANTITY ABBREV PQ TEXT

COL 105 106

ATTRIBUTE DOC DATE OF CHANGE COL 142 149

ATTRIBUTE COMPONENT ADDRESS ABBREV CA TEXT

KEYED COL 161 170

```

Figure 2.7. Build-Design Data Base Structure.

| S      | CN   | CP | СТ      | SR           | EN    | ET    | EP           | Pl |

|--------|------|----|---------|--------------|-------|-------|--------------|----|

| CLOCK1 | U001 | 13 | 54LS109 |              | U001  | JК    | J            | C  |

| CLOCK1 | CONN | 1  | CONN    | $\mathbf{T}$ | CONN  | CONN  | 1            | 0  |

| SIGA1  | CONN | 2  | CONN    | ${f T}$      | CONN  | CONN  | 2            | О  |

| SIGA1  | U002 | 1  | 54LS00  |              | U0021 | 2NAND | Α            | I  |

| SIGA2  | CONN | 3  | CONN    | ${f T}$      | CONN  | CONN  | 3            | 0  |

| SIGA2  | U002 | 2  | 54LS00  |              | U0021 | 2NAND | $\mathbf{B}$ | I  |

| SIGB1  | CONN | 4  | CONN    | ${f T}$      | CONN  | CONN  | 4            | О  |

| SIGBI  | U002 | 4  | 54LS00  |              | U0022 | 2NAND | $\mathbf{A}$ | Ι  |

| SIGB2  | CONN | 5  | CONN    | ${f T}$      | CONN  | CONN  | 5            | О  |

| SIGB2  | U002 | 5  | 54LS00  |              | U0022 | 2NAND | ${f B}$      | I  |

| RESET  | CONN | 6  | CONN    | $\mathbf{T}$ | CONN  | CONN  | 6            | 0  |

| RESET  | U003 | 13 | 5406    |              | U0036 | INV   | $\mathbf{A}$ | I  |

| SIGA   | U002 | 3  | 54LS00  | $\mathbf{T}$ | U0021 | 2NAND | $\mathbf{Y}$ | 0  |

| SIGB   | U002 | 6  | 54LS00  | T            | U0022 | 2NAND | Y            | 0  |

Figure 2.8. Build-Design Data Base for Sample Schematic.

cial purpose translator has been written to dump the DECsystem-20 based CAD system Build-Design data base into the HP DTS-70 form suitable for output into the HP DTS-70 system.

Case 2. Another instance of similar data content in different formats is the DECsystem-20 CAD Build-Design data base versus the Computervision (CV) Electrical Schematic-Printed Circuit (ES-PC) Data Base [CVPC83, CVDB83]. Ideally, the two systems should be capable of data interchange so that the CV system can be used for graphic data entry, display, and editing while the DEC-20 can be used for CPU-intensive computation involved in highly-dense digital printed circuit board physical

```

*HEADER

REVISED: <date>

MODULE: < module-name >

*LIB < model-lib-1> < model-lib-2>

*MAIN < title>$

*INPUTS

<input-connector-name>(<pin-loc-1>, <pin-loc-2>, ...

< pin-loc-n >)$

*OUTPUTS

<output-connector-name>(<pin-loc-1>, <pin-loc-2>, ...

< pin-loc-n >)$

*GATES

<input-connector-name>(<connector-type>)

<signal-name-1>.<pin-loc-1>

<signal-name-2>.<pin-loc-2> ...

<output-connector-name>(<connector-type>)

<signal-name-1>.<pin-loc-1>

<signal-name-2>.<pin-loc-2> ...

<component-name-I>

<component-address>(<component-type>)

<signal-name-1>.<pin-1> <signal-name-2>.<pin-2> ...

* < component-name-2>

<component-address>(<component-type>)

<signal-name-1>.<pin-1> <signal-name-2>.<pin-2> ...

* < component-name-n>

<component-address>(<component-type>)

<signal-name-1>.<pin-1> <signal-name-2>.<pin-2> ...

*END

Figure 2.9. Hewlett-Packard DTS-70 Pin-Signal Data Input Syntax.

```

design algorithms (e.g., routing).

The DEC-20 system data base (shown in Figure 2.7) is organized in a tabular format similar to the relational data model using System 1022<sup>TM</sup>, a data base management system from Software House [Soft84]. In addition to the Build-Design data base, component information is stored in a library contained in two principle data tables as shown in Figure 2.10: the Component Index table and the Component Pin table. This data is used for analyzing designs and for implementing a logical design into a physical layout with associated interconnect etch lines.

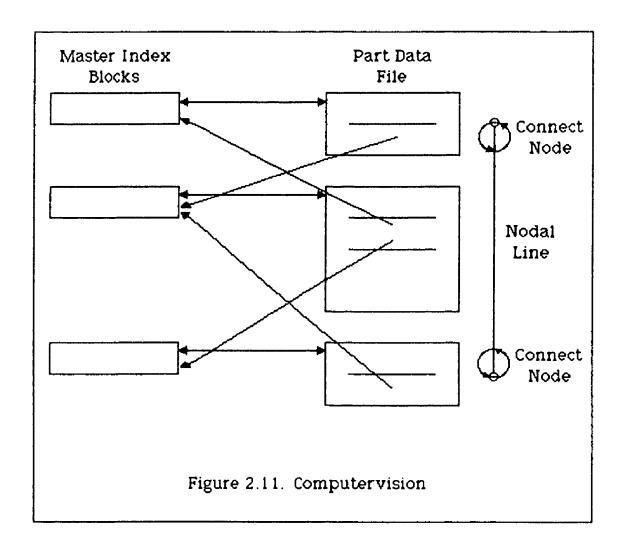

The CV ES-PC data base is organized into a Master Index of entities which are represented in detail within a Part Data File (PDF). Each entity represents a graphic element within a larger drawing. Parts are comprised of these elements and may be nested in a hierarchical manner in order to form more complex drawings. In fact, each drawing is just another part which is stored into the PDF and pointed to by the Master Index. Figure 2.11 lists the entities associated with the ES-PC application (2.1) on the CV. The orientation of the CV data is toward graphic presentation of the data. Even though there are analysis and some physical design functions which can be performed on the CV system, the magnitude of complexity which the CV system is capable of handling is much more limited in comparison to the DEC-20, due to CPU power differences. The CV system is well suited to editing of logic circuits using graphic representations, with

<sup>(2.1)</sup> The CV system is general-purpose and supports many other applications such as mechanical parts drawing, surveying, architecture, etc. While each application uses the same data base concept, the entities may be different.

#### Component Index Data

DEFAULT SIGNAL NAME

COMPONENT TYPE

PART DESIGNATOR

DESIGNATOR TYPE

PACKAGE CODE

DESCRIPTION

REMARK

# Component Pin Data

COMPONENT TYPE PART DESIGNATOR COMPONENT PIN CONNECTOR TEST POINT FEED THRU ELEMENT ADDRESS ELEMENT TYPE ELEMENT PIN PIN FUNCTION SOURCE PIN SWAP LOAD OVERRIDE CODE SIGNAL TYPE NO CONNECT

Figure 2.10. Hughes DEC-20 CAD System Data Base.

a straight-forward manipulation language entered via stylus and menu tablet.

The mapping from DEC-20 to CV data bases is complex in that the elements of a component or a schematic are not represented by unique entities on the CV system. Most of the data which should be shared between the two systems is textual in nature (e.g., signal names, pin functions, component names, etc The use of text on the CV system is rather unrestricted, and as a result, it is only by context that a textual data element on the CV system can be associated with a data element in the DEC-20 data base.

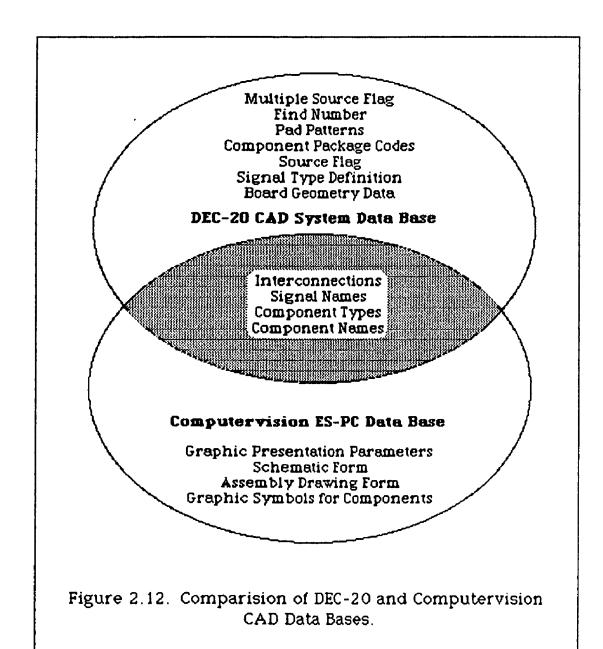

The difficulty is shown graphically by the intersection of the sets of data which each system maintains. This intersection represents only a fraction of either system as shown in Figure 2.12.

As these two cases illustrate, the same conceptual CAE/CAD/CAM data is represented in a variety of ways on different systems. The number of systems is increasing. In fact, it is quite difficult to list all of the commercial CAE/CAD/CAM systems. Adding to the complexity of the problem are custom, in-house systems which many electronics firms have developed to meet their special requirements.

#### 2.5 CAE/CAD/CAM Data Exchange Standards

Because the data transport problem is pervasive and wide-spread, a number of attempts have been made to standardize on neutral data base formats. However, these data standards do not completely address the data transport problem. The job of translating data to and from a standard is left up to the originator and receiver of the CAE/CAD/CAM data format being transported. The problem of what to do with data which cannot be expressed in the standard is not addressed.

Among the attempts at standardization are the Initial Graphics Exchange Specification (IGES), ANSI/IPC-D-350, and most recently the Electronic Design Interchange Format (EDIF). The preface to the EDIF specification [EDIF84] identifies the problems encountered by those attempting to define a standard:

"While many interchange formats and hardware description languages have been developed over the past decode, each has

suffered from one or more of the following drawbacks:

Narrow focus, ... Proprietary, ... Difficult to Implement, ... Difficult to Extend, ..."

A brief description of these standards will bring to light these drawbacks and illustrate others as well.

#### 2.5.1 Initial Graphics Exchange Specification (IGES)

The formulation of IGES dates back to late 1979. The first IGES concepts stemmed from a joint meeting of the Air Force, Army, Navy, and the National Bureau of Standards (NBS) held at the National Academy of Sciences on October 11, 1979. Presentations by CAD/CAM systems vendors, corporate systems designers, and standards groups pointed to problem in data transport between CAD/CAM systems. At this time and since then, the emphasis has been on 3D graphics CAD/CAM systems for mechanical design. It was generally agreed that an initial graphics exchange specification was needed immediately. [IGES80]

Later in 1979, a committee was formed between representatives from the NBS, Boeing, and General Electric. The Boeing and General Electric corporate CAD/CAM exchange systems were selected as initial systems upon which IGES was formed. Subsequent to its first release, IGES became an ANSI standard (ANSI Y14.26M-1981) issued on April 15, 1982.

Due to the rapid formulation of IGES, several misconceptions about the intent of IGES developed even prior to its first release. In an attempt to clarify IGES, the technical committee offered a list of statements describing IGES in the Introduction of the first release. Several of these statements point to inherent limitations built into the standard:

- IGES is designed with the technical aspects of several CAE/CAD/CAM systems in mind. Thus the translation from vendor systems to IGES and vice versa will not be one for one, but should be feasible.

- IGES is not a complete spec of all the data in all CAE/CAD/CAM systems. Thus, there may be a loss of data or structural information in the translation to and from IGES.

- IGES is based on the Boeing CAD/CAM Integrated Information Network, the General Electric Neutral Data Base, and a variety of other data exchange formats which were given to the committee.

- IGES is the best specification that could be produced in the time frame permitted. While it is not a copy of any of the exchange formats presented to the committee, it has the advantage of the experience and knowledge gained in their production and use.

- IGES is a set of geometrical, drafting, structural, and other entities. Thus it has the capability to represent a majority of the information in CAD/CAM systems.

- IGES is extensible. Several definition mechanisms have been provided to permit IGES to be expandable. A working com-

mittee has been set up to coordinate expansions and to correct errors.

- IGES is not designed for the technical aspects of any one of the currently available CAD/CAM systems.

- IGES is not perfect, or the solution to all data exchange problems between CAD/CAM systems.

- IGES is not a carbon copy of any of the exchange formats given to the technical committee.

It is clear, that the committee was attempting to deliver a spec in a short time-frame, and that they hoped to provide an extensible framework which would allow future additions to cover any initial shortcomings.

The initial format of an IGES file was a numerically sequenced set of 80-column card images in ASCII. As would be expected with graphics data bases, this file format resulted in very large IGES files. This problem resulted in the second release of IGES including an optional binary representation of an IGES file. The structure of the binary format is essentially the same as the ASCII format.

An IGES file consist of 5 sections: Start Section, Global Section, Directory Entry Section, Parameter Data Section, and Terminate Section. The Start Section contains comments about the IGES file and the part represented. The Global Section describes machine dependent characteristics used in an IGES file, various global delimiters, and units. The Directory Entry Section contains entity descriptions and pointers to parameters, other entities, line fonts, levels, views, translation/rotation matrices, status

flags. Entities are of three categories:

- Geometry: Circles, Lines, Conics, Points, etc.

- Annotation: Dimensions, Notes, Arrows, Witness Lines

- Structure: Associativity, Line Font, Macro, Subfigure, Text

Font, Drawing, Property, and View.

The Parameter Data Section contains end points, transformation matrix values, angles, and pointers. In general, all parametric data needed to describe entities defined in the Directory Entity section is contained in the Parameter Data section. The Terminate Section contains the card counts for each section and serves as a checksum of sorts to verify that the file has been transmitted properly.

While the basic structure of an IGES file doesn't appear too complicated, there are 20 geometric entities, 13 annotation entities, 12 structural entities, plus a macro capability. The majority of the entities (> 75%) are geared for the mechanical CAD/CAM field, where the emphasis has been since the early days of the IGES inception. The specification as issued (both versions 1.0 and 2.0) gives only one, incomplete example of how IGES is applied to electronic CAD/CAM systems. Much of IGES is oriented toward describing drawings and not to describing the content of the drawings. There is virtually no support for CAE data used in simulation and analysis models. Presumably, CAE is treated as a user extension.

There is an IGES subcommittee which has been actively addressing extending IGES for electronics data as recently as February 1984. Working documents and meeting minutes indicate that there are shortcomings in

IGES version 2.0 which could be resolved in a number of ways, including adding more entities to describe schematics. It appears that no single approach has been approved and that further committee discussion is required.

As regards the integration of IGES with other standards, the IGES Electrical/Electronic Subcommittee is aware of the existence of ANSI/IPC-D-350. In February 1984, the Subcommittee suggested that the IPC standard should be regarded as any other vendor. (2.2) Also, it was suggested that IGES should consider its role as a super-set of CAD/CAM data (including IPC). At the other extreme, there seems to be no formal or informal recognition of EDIF by the IGES Subcommittee to date. The EDIF effort began in late 1983 with the 0.8 version of the specification being released May 14, 1984 and version 0.9 on July 16, 1984.

Aside from the lack of development in the area of electronic design data, there are a number of other IGES deficiencies. Scowen [Scow82] indicates a fundamental problem with all systems which are based upon the transfer of drafting data. The information defines drawings of a product and not the product itself. Scowen argues that the "full benefits" of a standard can be realized only

"by complete integration based on a model of the product itself rather than a model of drawings of the product."

<sup>(2.2)</sup> Unpublished minutes of the IGES Electrical/Electronic Subcommittee Meeting of February 9, 1984.

Another problem Scowen identified is that some objects can be represented in several ways in IGES. For example, a rectangle may be a composite curve, a bounded plane, or a subfigure. The lack of a canonical representation for objects leads to difficulty in translating data to another system and then back again. In fact, it is difficult to check whether two IGES files are equivalent and describe the same object.

An early criticism of IGES was that IGES files were large. This was to a large extent a problem with the ASCII 80-column card image format. With version 2.0, IGES now has a binary format as well. Another problem with the IGES file format is that there is no facility for making easy corrections since all internal pointers are absolute. Consequently, if a change needs to be made to a design, a new IGES file must be written. If an IGES translator is expensive to run (which is likely), then the purpose of facilitating data transport is defeated.

It is clear that while IGES is a tremendous accomplishment, it is not a panacea.

# 2.5.2 ANSI/IPC-D-350

The purpose of the ANSI/IPC-D-350 [IPC77] standard is to provide a uniform means of describing printed wiring boards in a digital (80-column card) form. All aspects of printed wiring board designs can be documented using this standard including copper type, dielectric used, plating thickness, locations of lines, line widths, orthogonality restrictions, pads, drill holes, and layering schemes.

An IPC file contains 5 sections: Parameter Records, Comment Records, Feature/Location Records, Complex or Composite Records, and an End of Job Record. Parameter records include JOB, DIM, UNITS, TOL, LAYER, and IMAGE records which describe global values needed to interpret the IPC file. Within the comment record are included

- List of Features,

- Finished part descriptions fabrication materials and special instructions,

- Line Record Identification structure of line records, and

- References to specification documents.

The Feature/Locations records use a pseudo-assembler language to describe

- Op codes for continuation records, line records, point records, and annotation or lettering records;

- Features Description Areas which depend upon the op-code but include dimensions, layer codes, signal identification, hole size, annotation character height; and

- Location Description Areas which contains x-y data.

The Complex or Composites records contain op-codes for subroutine definitions and subroutine calls.

While the IPC standard is comprehensive in its treatment of PC board related data, the bulk of the electronic CAE/CAD data is not

covered by intent. Thus, this standard suffers from the "Narrow focus" drawback identified by the EDIF formulating Committee, although ANSI/IPC 350B was not specifically referenced.

## 2.5.3 Electronic Design Interchange Format (EDIF)

This format is the newest attempt to develop a universally acceptable standard for the transport of electronic design data. As indicated at the beginning of this section on data standards, EDIF was undertaken because shortcomings were perceived with all previous efforts. Several predecessors were mentioned by name, but IGES wasn't included. It is unlikely that IGES would be unknown to a committee with CAE/CAD/CAM system houses represented. It can only be assumed that the IGES effort in the area of electronic data is not regarded to be of importance to the EDIF committee.

The version 0.9 EDIF is quite comprehensive in its inclusion of all classes of electronic design data. The classes described in section 2.4 are addressed and to a more extensive level of detail in EDIF. The basic element of design is the "cell". Several "views" of a cell provide data regarding the schematic, symbolic layout, masks, behavior, and documentation. Provisions are mode for cell libraries and multiple technologies.

From a structural point of view, the EDIF file is expressed in LISP. Provisions are included for defining variables and macros, as well as conditionals. The EDIF syntax is quite extensible and allows for growth.

EDIF is oriented toward gate arrays and custom VLSI designs and provides for CAE as well as CAD/CAM data. However, some of the CAE data (e.g., simulation models) are expressed as comments. Clearly, EDIF is new and there are a number of features which are only developed superficially (e.g., the documentation view). Also, there have been a number of criticisms about some of the features of EDIF.

The source of the criticisms are the minutes of the July 16, 1984 public meeting on EDIF. Some have objected to the LISP syntax for efficiency reasons. The gate array description features of EDIF are unclear and confusing. The number of Test States is inadequate. The Behavioral description lacks power. There are weaknesses in the mapping among the logical, physical, and behavioral interfaces. In some cases information is duplicated as in the redundant definition of ports between views. There are other minor and subtle flaws which were discussed at the meeting. The intent of the discussion was to identify problems which need correction before the version 1.0 EDIF is released.

Because the EDIF effort is new, the issue of what to do in cases when data cannot be represented in EDIF has not really been discussed. The assumption made by the committee is that the user extension feature will cover these cases.

#### 2.5.4 Commercial Systems

In addition to standards which are provided to assist in data transport, there has been at least one commercial offering. Octal, Inc. of Mountain View, CA announced as early as October 1981 a product which converts CALMA drawing data bases into Applicon data bases. That particular system was reported <sup>(2.3)</sup> to log components of the data base which were "not exactly converted" due to differences in data representation.

Again as in the case of data standards, the problem of data which doesn't translate is acknowledged, but no obvious treatment prescribed. This problem among others is described in the next chapter and a methodology for CAE/CAD/CAM data transport is presented.